PIN光电二极管是在PN结的P型层和N型层之间夹了一层本征半导体(semiconductor ,形成P-I-N结构而得名,如下图所示:如上图所示,处于...

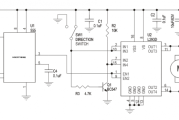

ECL门的电路实例

接线图

2023年07月21日 22:52 368

admin

1.TTL或非门

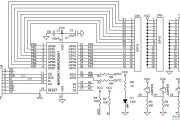

图1(a)表示TTL或非门的逻辑电路,图(b)是它的逻辑符号。或非逻辑功能是对TTL与非门的结构改进而来,即用两个BJT管T2A和T2B代替T2。若两输入端中有一个为高电平,则T2A和T2B均将截止,iB3=0,输出为高电平。若A、B两输入端中有一个为高电平,则T2A或T2B将饱和,导致iB3>0,iB3便使T3饱和,输出为低电平。这就实现了或非功能。即L=A+B=A·B。这个式子表明,图1(a)就正逻辑而言是或非门。

图1(a)表示TTL或非门的逻辑电路,图(b)是它的逻辑符号。或非逻辑功能是对TTL与非门的结构改进而来,即用两个BJT管T2A和T2B代替T2。若两输入端中有一个为高电平,则T2A和T2B均将截止,iB3=0,输出为高电平。若A、B两输入端中有一个为高电平,则T2A或T2B将饱和,导致iB3>0,iB3便使T3饱和,输出为低电平。这就实现了或非功能。即L=A+B=A·B。这个式子表明,图1(a)就正逻辑而言是或非门。

2. 集电极开路门(OC门)

所谓集电极开路是指TTL与非门电路的推拉式输出级中,删去电压跟随器,如图2(a)所示。为了实现线与的逻辑功能,可将多个门电路输出管T3的集电极至电源VCC之间,加一公共的上拉电阻RP,如图2(a)所示。为了简明起见,图中以两个集电极开路门并联为例。图(c)为其逻辑符号,其中图标“ ”表示集电极开路之意。

”表示集电极开路之意。

所谓集电极开路是指TTL与非门电路的推拉式输出级中,删去电压跟随器,如图2(a)所示。为了实现线与的逻辑功能,可将多个门电路输出管T3的集电极至电源VCC之间,加一公共的上拉电阻RP,如图2(a)所示。为了简明起见,图中以两个集电极开路门并联为例。图(c)为其逻辑符号,其中图标“

”表示集电极开路之意。

”表示集电极开路之意。

图2集电极开路(OC)门(a)OC门的输出级(b)由构成的线与逻辑原理图(c)逻辑符号

3.三态与非门(TSL门)

三态与非门的输出除了具有一般与非门的两种状态,即输出电阻较小的高、低电平状态外,还具有高输出电阻的第三状态,称为高阻态,又称为禁止态。

一个简单的TSL门的电路如图3(a)所示,图(b)是它的逻辑符号。其中CS为片选信号输入端,A、B为数据输入端。

图3三态与非门电路(a)电路图(b)逻辑符号

当CS=1时,TSL门电路中的T5处于倒置放大状态,T6饱和,T7截止,即其集电极相当于开路。此时输出与输入的逻辑关系与一般与非门相同。这种状态成为TSL的工作状态。但当CS=0时,T7导通,使T4的基极钳制于低电平。同时由于低电平的信号送到T1的输入端,迫使T2和T3截止。这样T3和T4均截止,门的输出端L出现开路,既不是低电平,又不是高电平,这就是第三工作状态。这样,当CS为高电平时,TSL门的输出信号送到总线,而当CS为低电平,门的输出与数据总线断开,此时数据总线的状态由其他门电路的输出所决定。

相关文章

发表评论