PIN光电二极管是在PN结的P型层和N型层之间夹了一层本征半导体(semiconductor ,形成P-I-N结构而得名,如下图所示:如上图所示,处于...

TTL逻辑门电路

1、基本的BJT反相器的动态性能

影响BJT开关速度的原因是BJT存储电荷,电荷的存储和消散需要一定的时间。当考虑负载电容对基本反相器的影响时,电路如图1所示。CL中包含门电路之间的接线电容以及门电路的输入电容。当反相器输出电压vo由低向高过渡时,电路由VCC通过RC对CL充电。反之,当v0由高向低过渡时,CL又将通过BJT放电。由于CL的充、放电过程均需经过一定的时间,因而增加了输出电压v0波形的上升时间和下降时间。特别是CL充电回路的时间常数RcCL较大时,v0上升较慢,即增加了上升时间。这使得反相器的开关速度很慢。

图1 带负载电容CL的BJT反相器

2、TTL反相器的基本电路

带电阻负载的BJT反相器,其动态性能不理想。因而,在保持逻辑功能不变的前提下,可以另外加若干元器件以改善其动态性能,如减少由于BJT基区电荷存储效应和负载电容所引起的时延。这需改变反相器输入电路和输出电路的结构,以形成TTL反相器的基本电路。

图2表示TTL反相器的基本电路,该电路由三部分组成,即BJTT1组成电路的输入级,T3、T4和二极管D组成输出级,以及由T2组成的中间级作为输出级的驱动电路,将T2的单端输入信号V12转换为互补的双端输出信号。以驱动T3和T4。

图2 TTL反相器的基本电路

1. TTL反相器的工作原理

(1)当输入为高电平,如vI=3.6V时,电源VCC通过Rb1和T1的集电结向T2、T3提供基极电流,使T2、T3饱和,输出为低电平,vo=0.2V。此时

VB1=VBC1+VBE2+VBE3=(0.7+0.7+0.7)V=2.1V

显然,这时T1的发射结处于反向偏置,而集电结处于正向偏置。所以T1处于发射结和集电结倒置使用的放大状态。由于T2和T3饱和,输出VC3=0.2V,同时可估算出VC2的值:

VC2=VCES2+VB3=(0.2+0.7)V=0.9V

此时,VB4=VC2=0.9V。作用于T4的发射结和二极管D的串联支路的电压为VC2-VO=(0.9-0.2)V=0.7V,显 然,T4和D均截止,实现了反相器的逻辑关系:输入为高电平时,输出为低电平。

(2)当输入为低电平,vI=0.2V时,T1的发射结导通,其基极电压等于输入低电压加上发射结正向压降,即

VB1=(0.2+0.7)V=0.9V

此时VB1作用于T1的集点结和T2、T3的发射结上,所以T2、T3都截止,输出为高电平。

由于T2截止,VCC通过RC2向T4提供基极电流,致使T4和D导通,其电流流入负载。输出电压为

vO≈VCC-VBE4-VD=(5-0.7-0.7)V=3.6V

显然:输入为低电平时,输出为高电平。

2. 采用输入级以提高工作速度

当TTL反相器输入电压由高(3.6V)变低(0.2V)的瞬间,VB1=(0.2+0.7)V=0.9V。但由于T2、T3原来是饱和的,它们的基区存储电荷还来不及消散,在此瞬间,T2、T3的发射结仍处于正向偏置,T1的集电极电压为

VC1=VBE2+VBE3=(0.7+0.7)V=1.4V

此时,T1的集电结为反向偏置,因输入为低电平时,T1的发射结为正向偏置,于是T1工作在放大区,这时产生基极电流iB1,其射极电流β1iB1流入低电平的输入端。集电极电流iC2≈β1iB1的方向是从T2的基极流向T1的集电极,它很快地从T2的基区抽走多余的存储电荷,使T2迅速地脱离饱和而进入截止状态。T2的迅速截止导致T4立刻导通,相当于T3的负载是个很小的电阻,使T3的集电极电流加大,多余的存储电荷迅速从集电极消散而达到截止,从而加速了状态转换。

3. 采用推拉式输出级以提高开关速度和带负载能力

图2采用了由T3、T4组成推拉式输出级。其中T4组成电压跟随器,T3为共射极电路,作为T4的射极负载。这种输出级的优点是,既能提高开关速度,又能提高带负载能力。

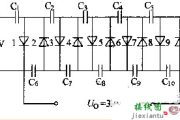

3、TTL与非门电路

图2所示的基本TTL反相器不难改变成为多输入端的与非门。它的主要特点是在电路的输入端采用了多发射极的BJT。器件中的每一个发射极能各自独立地形成正向偏置的发射结,并可促使BJT进入放大或饱和区。两个或多个发射极可以并联地构成一大面积的组合发射极。

图3(a)说明采用多发射极BJT用作3输入端TTL与非门的输入器件。当任一输入端为低电平时,T1的发射结将正向偏置而导通,T2将截止。结果将导致输出为高电平。只有当全部输入端为高电平时,T1将转入倒置放大状态,T2和T3均饱和,输出为低电平。

图3(b)为3输入端TLL与非门的逻辑符号。

图3具有多发射级BJT的3输入端与非门电路(a)电路图(b)逻辑符号

相关文章

发表评论