这里介绍的项目是一个模拟电容式接近传感器。该电路来自德州仪器 (TI 应用笔记。大多数传统电容式接近传感器产生“1”或“0”输出,该电路产生直流输出,...

数字时钟电路原理图分析

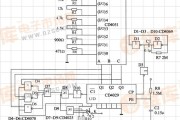

数字钟的计数电路是用两个六十进制计数电路和一个十二进制计数电路实现的,但是考虑到对74LS90比较熟悉,用两个74LS90来分别控制秒和分的十位和个位。个位采用十进制,十位采用六进制就能完美解决六十进制的秒计数。

一、

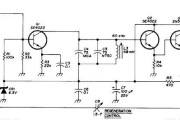

时钟电路:(a)内部方式时钟电路,(b)外接时钟电路

在内部方式时钟电路中,必须在XTAL1和XTAL2引脚两端跨接石英晶体振荡器和两个微调电容构成振荡电路,通常C1和C2一般取30pF,晶振的频率取值在1.2MHz~12MHz之间。对于外接时钟电路,要求XTAL1接地,XTAL2脚接外部时钟,对于外部时钟信号并无特殊要求,只要保证一定的脉冲宽度,时钟频率低于12MHz即可。

晶体振荡器的振荡信号从XTAL2端送入内部时钟电路,它将该振荡信号二分频,产生一个两相时钟信号P1和P2供单片机使用。时钟信号的周期称为状态时间S,它是振荡周期的2倍,P1信号在每个状态的前半周期有效,在每个状态的后半周期P2信号有效。CPU就是以两相时钟P1和P2为基本节拍协调单片机各部分有效工作的。

二、

由图可以看出,当“时”个位U8计数输入端到第10个触发信号时,U8计数器复零,进位端QD向U7“时”十位计数器输出进位信号,当第24个“时”(来自“分”计数器输出的进位信号)脉冲到达时,U8计数器的状态为“0100”,U7计数器的状态为“0010”,此时“时”个位计数器的QC和“时”十位计数器的QB输出为“1”。把他们分别送入U7、U8计数器的清零端R01和R02,通过74LS290内部的R01和R02与非 13实现。

三、

校“时”和校“分”的校准电路是相同的,今以校“分”为例。“与非”门G1、G2、G3构成一个二选一电路。正常计时时,通过基本RS触发器打开“与 非”门G1而封闭G2门,这样秒计数器输出的脉冲可经G1、G3进入分计数器,而此时G2由于一个输入端为0,校准用的秒脉冲进不去。在校准“分”时,按 下开关S1,情况正好适反:G1被封门而G2打开,标准秒脉冲直接进入分计数器进行快速校“分”。

审核编辑:彭菁相关文章

发表评论