场效应晶体管放大器是电压控制器件,具有输入阻抗高、噪声低的优点,被广泛应用在电子电路中,特别是具有上述要求前级放大器显示器出越性。根据场效应管两大类型...

嵌入式电路设计(嵌入式语音识别电路/三极管基础电路/嵌入式硬件电路)

在嵌入式电路设计中包含模拟电路设计成分比较少,常用的模拟器件大部分为二极管、晶体管。

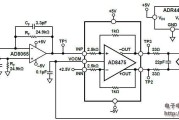

一、嵌入式语音识别电路

LD3320的内部集成了快速稳定的优化算法,不需外接Fla-sh、RAM,不需要用户事先训练和录音而完成非特定人语音识别,识别准确率高。图中,LD3320采用并行方式直接与 STM32F103C8T6相接,均采用1kΩ电阻上拉,A0用于判断是数据段还是地址段;控制信号,复位信号以及中断返回信号INTB与 STM32F103C8T6直接相连,采用10kΩ电阻上拉,辅助系统稳定工作;和STM32F103C8T6采用同一个外部8 MHz时钟;发光二极管D1、D2用于复位后的上电指示;MBS(引脚12)作为麦克风偏置,接了一个RC电路,保证能输出一个浮动电压给麦克风。

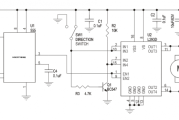

二、三极管基础电路

该电路为晶振关闭功能电路,其中VO接MCU晶振输入端如(XIN)。

若Q1和Q3基极同时为低时,Q2导通而使得VO为0造成晶振停振关闭处理器。我们分析R3和R4(实际电路470K)使得Q2和Q3处于饱和态;Q3为Q1集电极负载,调整R5阻值时可控制Q1处于饱和态或放大态。要使Q2基极导通必须使Q1提供足够大电流才满足条件,只有Q1处于放大态才满足条件。

三、嵌入式硬件电路

(1)上拉、下拉电阻:考虑用内部或者外部上/下拉电阻,内部上/下拉阻值一般在 700Ω 左右,低功耗模式不宜使用。外部上/下拉电阻根据需要可选 10KΩ~1MΩ 之间。

(2)开关量输入:一定要保证高低电压分明。理想情况下高电平就是电源电压,低电平就是地的电平。如果外部电路无法正确区分高低电平,但高低仍有较大压差,可考虑用 A/D 采集的方式设计处理。对分压方式中的采样点,要考虑分压电阻的选择,使该点通过采样端口的电流不小于采样最小输入电流,否则无法进行采样。

相关文章

发表评论