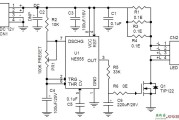

设计汽车转换器时,尺寸、成本和可靠性是关键因素。为了满足这些标准,最简单的双向拓扑;选择同步降压/反向升压转换器。最大限度地提高能源效率也至关重要,在...

2位模数转换器电路

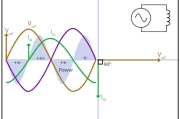

接线图

2023年07月23日 06:31 301

admin

这将为我们提供模拟输入所有四个可能值的 2 位输出代码:

这将为我们提供模拟输入所有四个可能值的 2 位输出代码:2 位 A/D 转换器输出

其中:“X”是“无关”,即逻辑“0”或逻辑“1”条件。

其中:“X”是“无关”,即逻辑“0”或逻辑“1”条件。那么这个模数转换器是如何工作的呢?为了使 A/D 转换器发挥作用,它必须产生模拟输入信号的有意义的数字表示。在这个简单的 2 位 ADC 示例中,为简单起见,我们假设输入电压 V IN介于 0 到 4 伏之间,因此设置 V REF和电阻分压器网络以在每个电阻器上降低 1 伏。

当 V IN介于 0 和 1 V 之间时,(<1V) 所有三个比较器上的输入都将小于参考电压,因此它们的输出将为低电平,编码器将在引脚 Q 0 上输出二进制零 (00)条件和问题1。当V IN增加并超过1伏但小于2伏时,(1V

因此,现在当 V IN增加到下一个参考电压电平 2 伏以上时,比较器 U2 会检测到变化并产生高输出。但由于输入 D 2 的优先级高于输入 D 0或 D 1,因此优先级编码器输出二进制“2”(10)代码,依此类推,当 V IN超过 3 伏时,产生二进制代码输出“3”( 11)。显然,当 V IN在每个参考电压电平之间减小或变化时,每个比较器都会向编码器输出高电平或低电平条件,编码器进而产生相对于 V IN 的 00 和 11 之间的 2 位二进制代码。

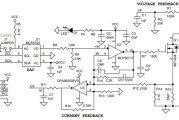

这一切都很好,但优先级编码器不能用作 4 至 2 位设备,如果我们使用市售的编码器,例如 TTL 74LS148 或其 CMOS 4532 等效产品,它们都是 8 位设备,则 6的二进制位将不会被使用。但是,可以使用数字异或门和信号二极管矩阵来制作简单的编码器电路,如图所示。

使用二极管的 2 位 ADC

这里,比较器的输出在馈送到二极管之前使用异或门进行编码。两个外部下拉电阻器用于其输出和接地 (0V),以确保低电平条件并在二极管反向偏置时阻止输出浮动。

这里,比较器的输出在馈送到二极管之前使用异或门进行编码。两个外部下拉电阻器用于其输出和接地 (0V),以确保低电平条件并在二极管反向偏置时阻止输出浮动。与前一电路一样,根据 V IN的值确定哪个比较器向异或门产生输出信号高电平(或低电平),如果一个输入或另一个输入为高电平(但不是两者都为高电平),则产生高输出, (布尔表达式为 Q = A .B + A. B)。这些异或门也可以使用组合逻辑“与-或-与非”门来构造。

4 至 2 转换器的两种设计的问题在于,这个简单的 2 位 A/D 转换器的分辨率为 1 伏,因为正如我们所见,V IN处的模拟输入电压必须在命令编码器更改其输出代码。提高输出分辨率的一种方法是使用更多比较器将其增加到 3 位 A/D 转换器。

相关文章

发表评论