详解加法器的电路实现 基本思路:想个办法把三排开关连起来输入信息:输出信息实现:异或门实现和运算;实现与门进位操作;并行封装一个异或门和一个与门是半加...

加法器电路,简易反相器电路图

曼彻斯特加法器原理

曼彻斯特加法器原理是一种产生数字和的装置。加法器和加数是输入,半加法器是输出和与进位的器件。如果加数相加,输入加数和低位的数字,输出和与进位,就是全加器。曼彻斯特加法器是一种电流并行负反馈放大器。信号输入到运算放大器的反相输入端,输出电压的一部分反馈到运算放大器的反相输入端,形成电流并联负反馈放大电路。其输入信号仅为差模信号,因此抗干扰能力强。加法器是一种产生数字总和的装置。加法器和加数是输入,半加法器是输出和与进位的器件。如果加数相加,则加数的数字和低位数字是输入,而和与进位是输出,它们是全加器。通常用作计算机算术逻辑单元,执行逻辑运算、移位和指令调用。在电子学中,加法器是一种数字电路,可以将数字相加。使用三个代码,主加法器以二进制运算。因为负数可以用二的补码来表示,所以不需要加减。

设计一个加法器?

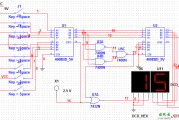

1.半加法器半加法器是用一位计算两个二进制数A和B的和,输出结果是sum(s)和carry(c)。在多位数的计算中,进位C将作为下一个相邻位的加法。单个半加法器的计算结果为2c s .真值表:逻辑表达式:Verilog描述为:MoleHalf _ Adder (input a,input b,output c,outputs);赋值c=ab assign s=a^b;endmole的电路图如下:二。全加器。与半加法器不同,全加器具有进位cin。输入是A、B、cin,输出是sum(s)和carry(c),都是单比特信号。是三个单比特数s,b,cin之和,cout是a,b,cin三个数超过2后的进位。真值表逻辑表达式:verilog描述:molfulladd(输入a,输入b,输入cin,输出cout,输出);赋值s=a^b^cin;assign cout=ab |(a^b CIN);Endmole电路图:符号:III。行波进位加法器N位加法器可按1位全加器组合。每个全加器的输出进位cout用作下一个全加器的输入进位cin。这个加法器叫做纹波进位加法器(简称RCA)。例如,16位加法器的结构如下所示,其中A和B是16位加数,S是A和B的和,c16是该加法器的输出。从上图可以看出,进位c16的结果取决于C15、C14和RCA。因此行波进位加法器的设计简单,只需要级联全加器即可,但其缺点在于进位链长,限制了加法器的性能。摩尔rca #(宽度=16)(输入[宽度-1:0] A,输入[宽度-1:0] B,输出[宽度-1:0] sum,输出cout);电线[宽度:0]温度;赋值temp[0]=0;genvar I;for(I=0;电话号码

串行进位加法器电路和超前进位加法器有何区别,它们各有什么优点?

串行进位从最低位到最高位相加,即整个进位分几个步骤进行。优点,电路结构简单。缺点,运行速度慢。所有提前的数字同时进位。一个CP脉冲可以完成整个进位过程。优点,运算速度快,缺点,电路复杂。

全加器的工作原理

全加器的英文名是full-adder,是由门电路将两个二进制数相加并求和的组合电路,称为一位全加器。一位全加器可以处理低阶进位,输出标准加法进位。多位全加器可以通过级联多个全加器来获得。常用的二进制四位全加器74LS283。一位全加器(FA)的逻辑表达式为:s=abCIN;Cout=ab+bcin+acin,其中A、B为要相加的数,cin为进位输入;s为sum,Co为进位输出;如果要实现多位加法,可以级联,也就是串联使用。比如32位和32位需要32个全加器;这种级联就是串行结构的慢速度。如果要快速并行加法,可以使用进位加法。如果用A和B的组合函数Xi和Y(受S0 … S3控制)代替全加器的输入,然后用全加器把X,Y和数字完全相加,就是ALU的逻辑结构。X=f (a,b);Y=F (a,b)不同的控制参数可以得到不同的组合函数,因此可以实现各种算术运算和逻辑运算。扩展信息:有了全加器,构造加法器非常容易。假设有A3A2A1A0和B3B2B1B0,用全加器构造A3A2A1A0 B3B2B1B0串行进位加法器的电路图。其中C-1=0,因为它是最低位,没有进位。这种串联方式只是完成了基本的功能,但从效率上来说完全不可行。假设全加器中各元件的时延为T,则全加器的时延为2t(见全加器电路图)。对于4位加法器,按照这种串联方式,加法器构造方法1图中最右边(最低位)全加器的计算完成后,才能计算右边两个全加器,以此类推。因此,4位加法器至少需要4*2t=8t的延时;如果是32位,就是64t的延迟。显然,这个加法器的效率与参与计算的二进制数的长度成正比。数字越长,延迟时间越长。在现代计算机中,不可能使用如此低效的加法器。只要梳理一下Ci和运算中涉及的两个4位二进制数的关系就可以了。它是用直接替换法发展而来的:在这个关系式中,直接列出了4位二进制加法的最后进位。不用等低位计算,直接计算高位,最后得到进位加法器的电路图。假设超前进位加法器中每个门的延迟为T,对于4位加法,最大延迟为4 T,即使增加更多位,延迟也是4t,比较串行进位加法器和超前进位加法器,前者电路简单,延迟与参与计算的二进制串长度成正比,而后者电路复杂,延迟为固定值。一般32位二进制字符串可以分组,每组8位。超前进位加法器用于组内加法,串行进位用于组间进位。这种折中的方法既保证了效率,又降低了内部电路的复杂度。来源:百度百科-全加器

相关文章

发表评论