描述 通过使用 OPA615 高带宽、直流恢复电路,此参考设计可为各种应用提供高带宽、高精度采样保持电路。该电路具有整套设计指南支持,...

采样保持电路图(五款采样保持电路设计原理图详解)

采样保持电路(采样/保持器)又称为采样保持放大器。当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。采样保持电路即为实现这种功能的电路。

采样保持电路能够跟踪或者保持输入模拟信号的电平值。在理想状况下,当处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化;当处于保持状态时,采样保持电路的输出信号保持为接到保持命令的瞬间的输入信号电平值。当电路处于采样状态时开关导通,这时电容充电,如果电容值很小,电容可以在很短的时间内完成充放电,这时,输出端输出信号跟随输入信号的变化而变化;当电路处于保持状态时开关断开,这是由于开关断开,以及集成运放的输入端呈高阻状态,电容放电缓慢,由于电容一端接由集成运放构成的信号跟随电路,所以输出信号基本保持为断开瞬间的信号电平值。

采样保持电路图设计(一)

采样保持放大器SMP04用做多路输出选择器电路图

如图所示为SMP04用做多路输出选择器,与解码器、D/A转换器构成的四路数字-模拟转换电路。数字信号输入模数转换器DAC8228,输出产生5~10V模拟电压送副SMP04,地址输入通道解码器,不同的地址解码后分别控制四路开关,以分别输出四模拟信号。采用DAC8228产生DAC电压输出可以使电路得以最大的简化。为了将输出电压干扰减小到最小,在采样信号被确认之前,必须保证有5μs的最后电压建立时间。每一个采样保持放大器必须在每一秒钟或更低时问刷新一次,以确保输出电压下降率不超过10mV或1/2LSB(最小有效位)。

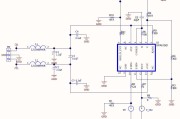

采样保持电路图设计(二)

如图所示为由SMP04与运放构成的增益为10的采样保持放大电路。电路中将SMP04置于运放OP490的反馈回路中,当S非/H=0时,SMP04内部开关闭合,运放OP490的反馈回路接通,电路增益由运放本身及反馈电阻决定,图中增益设置为10,输出端输出放大后的采样电压。当S非/H=1时,SMP04内部开关断开,运放OP490反馈回路也无法形成,输出端输出保持在内部保持电容上最近一次的采样电压,且不受输入端信号影响。运放输出端的两个二极管1N914起钳位作用,防止当SMP04保持状态时造成运放饱和。

标签: 采样保持电路

相关文章

- 详细阅读

- 详细阅读

-

采样保持电路图设计(四) - 采样保持电路图(五款采样保持电路设计原理图详解)详细阅读

采样保持电路图设计(四) 将一个经典的模拟累加器与一个采样保持放大器级联对一组模拟电压的采样进行保持。经典的模拟累加器是一个运放加上至少三只...

2023-09-27 215 采样保持电路

-

采样保持电路图设计(三) - 采样保持电路图(五款采样保持电路设计原理图详解)详细阅读

采样保持电路图设计(三) lf398峰值采样保持电路 1.lf398的峰值保持电路 图1:峰值保持电路原理图 峰值保持电路...

2023-09-27 320 采样保持电路

发表评论