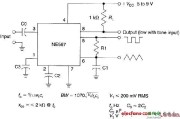

NE567组成的音调译码电路说明了NE567作为音解码器的作用。NE567组成的音调译码电路:...

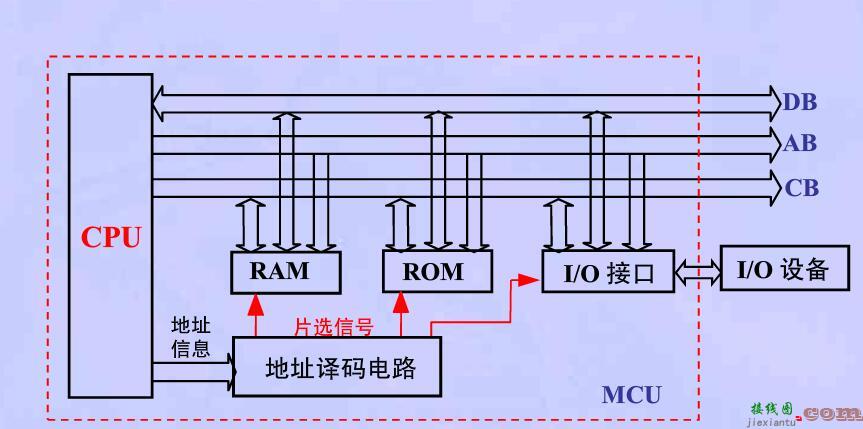

地址译码电路设计实验报告

地址译码方式

地址译码有两种方式,一种是单译码方式,或称为字结构方式;另一种是双译码方式,或称为X-Y译码结构。

1)单译码方式

16字×4位的存储器共有64个存储单元,排列成16行×4列的矩阵,每个小方块表示一个存储单元。电路设有4根地址线,可寻址24=16个地址逻辑单元,若把每个字的所有4位看成一个逻辑单元,使每个逻辑单元的4个存储单元具有相同的地址码,译码电路输出的这16根字线刚好可以选择16个逻辑单元。每选中一个地址,对应字线的4位存储单元同时被选中。选中的存储单元将与数据位线连通,即可按照要求实现读或写操作了。

2)双译码结构

视每个字的1位存储单元构成一个逻辑单元,图中每个小方块表示一个逻辑单元。16个可寻址逻辑单元排列成4×4的矩阵,为减少地址译码电路的输出数量,采用双重译码结构,每个地址译码的输出线数为22=4根(单译码方式需16根地址输出线)。图中A0、A1是行地址码,A2、A3是列地址码。行、列地址经译码后分别输出4根字线X0~X3和Y0~Y3。X字线控制矩阵中的每一行是否与位线连通,一行中究竟哪个逻辑单元被选中则由Y字线控制。被选中的单元将与数据线连通,以交换信息。

地址译码电路

地址译码电路设计实验报告

一、 实验目的

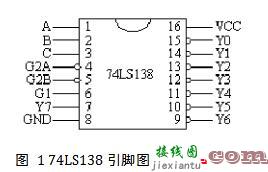

(1) 学习3-8译码器在接口电路中的应用;

(2) 掌握地址译码电路的一般设计方法。

二、 实验内容

用74LS138译码器设计地址译码电路,并用其输出作为基本输入输出单元的片选信号,使用设计的端口地址编写程序,实现数据的输入输出。

三、 实验原理

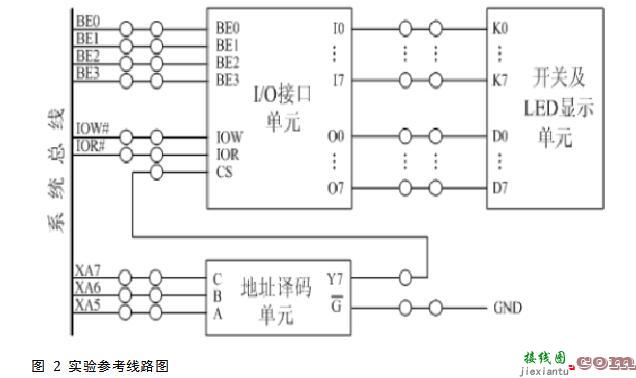

32位总线地址是由XA2开始,所以地址是以4字节边界对齐的。实验系统的I/O地址空间共有256字节,偏移地址一般从00H~FFH。起始地址由PC机系统分配,可以查看端口资源得到起始地址。所以设计地址译码电路,主要是针对XA7以下低8位地址线译码,得到偏移在00H~FFH之间的端口。本实验要求不使用总线上的片选信号,自行设计端口偏移地址为E0H~FFH的译码电路,然后用译码输出作为I/O接口单元的片选。编写程序,完成I/O数据操作。实验参考线路如图2所示。

四、 实验步骤

1、安装驱动,配置实验环境。驱动安装成功后,如图 3、图 4所示:

2、按图 2所示,连接实验线路,接好的线路如图5所示:

3、运行Tdpit集成操作软件,根据实验内容,编写实验程序,对实验程序进行编译、链接;

4、运行程序,拨动开关,观看数据灯显示是否正确。

五、 实验结果

1、程序下载到实验箱后,数据灯示55H,效果如图 6所示:

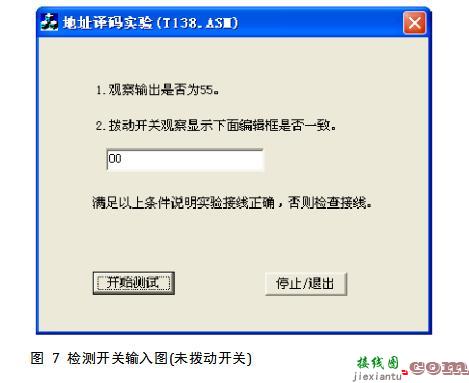

2、通过TdPit集成操作软件,检测由开关输入的值。未拨动开关时,检测结果如图 7所示,结果正确。

六、实验总结

本次实验不难,但需要一颗细致的心。连接电路是一个细致的活,经过几次检测线路,才发现线路问题,经过重新连接电路,得到预期效果。

标签: 译码电路

相关文章

发表评论