LBl0427A是一种通信用单片微电脑集成电路,应用于来电显示电话机中。 1·功能特点 LBl0427A集成电路内含脉冲/双音频信号发生器、液...

正弦波信号发生器基本原理与设计

正弦信号发生器主要由两部分组成:正弦波信号发生器和产生调幅、调频、键控信号。正弦波信号发生器采用直接数字频率合成DDS技术,在CPLD上实现正弦信号查找表和地址扫描,经D/A输出可得到正弦信号。具有频率稳定度高,频率范围宽,容易实现频率步进100Hz。

1、正弦波形的产生

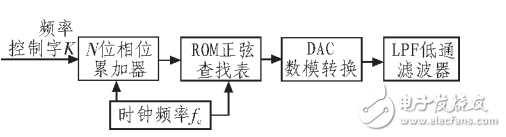

单向DDS由Nbit相位累加器和ROM只读存储器(正弦查找表)构成的数控振荡源(NCO),数模转换器(DAC)、低通平滑滤波器(LPF)构成,图1所示为DDS的基本结构。

图1 基于DDS技术的正弦信号发生器原理框图

图1中fc为时钟频率,K为频率控制字,N为相位累加器的字长,M为ROM地址线位数,L为ROM数据线宽度,f0为输出频率。相位累加器由全加器和累加寄存器级联组成。在时钟频率fc的控制下,对输入频率控制字K进行累加,累加满量时就产生溢出。相位累加器的输出对应于该时刻合成周期信号的相位,并且这个相位是周期性的,在0~2π范围内变化。相位累加器位数为N,最大输出为2N-1,对应于2π的相位,累加1次就输出1个相应的相位码,地址以查表方式,得到对应相位的信号幅度值,经过数模转换,就可以得到一定频率的信号输出波形,低通滤波器对输出的信号波形进行平滑处理,滤除杂波和谐波。

由于控制字K经过2N/K次累加,相位累加器满量溢出,完成1个周期运算,所以输出频率f0由fc和K共同决定,即f0=fcK/2N且K《2N-1,得到DDS的最小分辨率可达fc/2N。理论上通过设定DDS相位累加器的位数N、频率控制字K和时钟频率fc的值,就可以产生任一频率的输出。根据频率步进100Hz的要求,选取累加器的位数为19位,计算出时钟频率fc应为52.4288MHz。步进的累计误差通过软件补偿的方法进行修正,利用现有的52.4160MHz晶振完全精确地实现步进100Hz的要求。

2、产生模拟幅度调制信号

用调制信号去控制高频振荡的幅度,使其幅度的变化量随调制信号成正比地变化,这一过程称为幅度调制。若载波为uc=Uccosωct,调制信号为f(t)=cosΩt,则调幅波为

uAM(t)=Uc[1+macosΩt]cosωct(1)

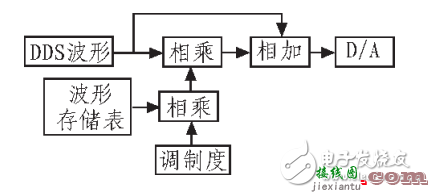

普通调幅波利用模拟相乘器实现,但是外围电路复杂,改变调制度需改变电路元件的参数,实现起来繁琐。可以采用CPLD芯片结合DDS技术灵活的实现数字调幅,原理如图2所示。

图2 幅度调制原理框图

由DDS产生的波形信号作为载波,在单片机内部作调制信号为1kHz的正弦波形存储表,根据键盘所设定的调制度ma(10%~100%)与存储表中的数据相乘的结果送CPLD与DDS得到的波形相乘,再与DDS信号相加就产生相应的数字调幅波编码,经D/A转换得到模拟调幅信号。

3、产生模拟频率调制信号

在连续波调制中,载波可表示为uc=Uccosωct,调制信号为UΩ(t),调频波是瞬时频率的变化量与调制信号成正比,因此调频波的瞬时角频率除了载波角频率ωc外,还附加一项和调制信号成正比的部分ω(t)=ωc+Δωf(t),Δωp(t)=kfuΩ(t),式中kf为比例系数,是单位调制信号强度引起的频率变化。Δωf(t)的最大值Δωf称为最大频偏,反映在频率上为f(t)=fc+Δfcos(2πft),调频波的表达式:

UFM(t)=Uccos[(fc+Δfcos(2πft)t](2)

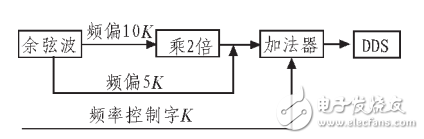

图3 频率调制原理框图

图3为CPLD数字调频电路,频偏为5K时的控制字是50,将余弦波形与50相乘,并与单片机传递的频率控制字相加,送入DDS模块经D/A转换就可以输出调频波,其设计原理图如图4所示。

图4 频率调制设计原理图

相关文章

发表评论