电路说明:CMOS电路直接驱动来自两个缓冲输出的任何一个的5 TTL负荷。该电路的工作频率是10MHz,是一个与CMOS兼容的两极场效应管。 ...

带隙基准电路_cmos无运放带隙基准源

常规的带隙基准电路

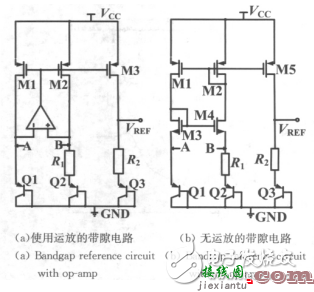

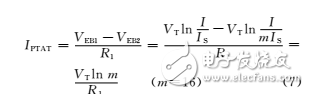

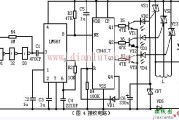

图1所示是两种常规的带隙基准电路,两者都是通过箝制A,B点电压相等,产生PTAT电流,再通过电阻R2将该电流转变为电压,与晶体管的VEB相加,得到基准电压。两者不同点是图1(A)所示电路使用运算放大器,图1(B)所示电路使用电流镜,使A,B电压相等。运放带隙基准的性能受运算放大器的失调电压、电源抑制比、增益等的严重影响。虽然可以通过仔细设计运算放大器得到很好的性能,但是运算放大器不仅引入了新的噪声和功耗,而且还增加了设计难度。电流镜带隙基准电路虽然没有使用运算放大器,但是因为沟道调制效应等原因,也会造成基准源精度的降低。

图1两种常规的带隙基准电路

cmos无运放带隙基准源

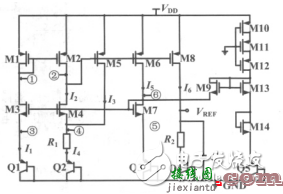

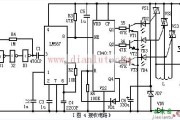

本文在图1(B)常规电流镜带隙基准电路的基础上,提出一种新型带隙基准电路,如图2所示。

图2 新型带隙基准电压源

启动电路

因为带隙电路中存在简并偏置点,当电源上电时,有可能出现所有支路都传输零电流的情况,使整个电路不能正常工作。因此,需要启动电路让电路在上电时摆脱简并偏置点。

图2电路中的M9~M14和Q5组成启动电路。刚接通电源时,节点⑥为低电平。M9导通,给节点⑥充电。当节点⑥电压升到一定高度时,整个带隙基准电路开始正常工作,同时导致(6)式成立,从而在电路正常工作时M9处于截止状态。启动电路不再对电路产生影响,完成电路的启动。

基准电压产生电路

图2中,M1,M2,M5,M6宽长比的比例为2∶1∶1∶2。M3,M4,M7宽长比的比例为2∶1∶2。Q1,Q3~Q5是一样的三极管,Q2是与Q1一样的16个三极管的并联。

M1~M5,Q1,Q2形成PTAT电流产生电路。M5还起反馈作用。M6,M7,Q3支路为M3,M4提供偏置电压,同时起负反馈作用,使节点①电压等于节点②电压。Q1和Q3是一样的三极管,M7和M3的栅极相连,使V⑤=V③。假设节点③电压不等于节点⑤电压,如果V⑤>V③,由VBE1<VBE3得到I1<I5,而由VGS3>VGS7得到I1>I5,与前面得到的结论相矛盾,所以,V⑤=V③,I1=I5,VGS1=VGS6,从而得到节点①电压等于节点②电压。由电流镜和各个晶体管的尺寸比值,可得出IPTAT=I1=I2+I3=I4=I5=I6。因为M3和M4传输同样的电流,漏极电压又相等,它们接在同一个栅极电压上,所以,V④=V③。

(7)式得到的正温度系数电流IPTAT被镜像到M8,Q4,R2支路。通过该电流流过R2产生的电压和VEB4相加,得到所要的带隙基准电压。

但是,实际电路会与这个比值有所偏差。最终电路得到了约1.25V的基准电压。

下面分析电路中两个支路的反馈作用。

首先分析2M6M7所在反馈支路。假设节点2电压升高V,节点6电压变化为:

由(14),(15)式得,V经过M5支路反馈后返回到节点2的电压变化量为:

从(13)和(16)式可以看出,这两个支路反馈回来的电压量V2均与-V成正比,所以是负反馈。这两路负反馈使电路比普通结构有更大的环路增益,从而提高了环路的抗干扰能力和电路的电源抑制比,减小了常规结构中沟道调制效应对基准源精度的影响。

相关文章

发表评论