用74ls138设计全加器 两个二进制数之间的算术运算无论是加、减、乘、除,目前在数学计算机中都是化作若干步加法运算进行的。因此...

用74ls138构成时序脉冲分配器

接线图

2023年01月06日 19:09 1214

admin

用74ls138构成时序脉冲分配器

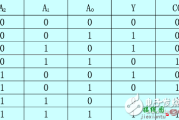

74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V。

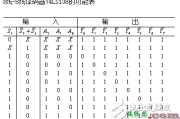

①当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。(即输出为Y0至Y7的非)比如:A2A1A0=110时,则Y6输出端输出低电平信号。

②利用 E1、E2和E3可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

③若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

④可用在8086的译码电路中,扩展内存。

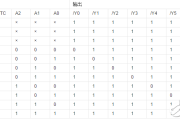

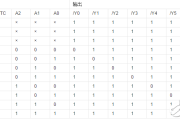

时序脉冲分配电路连接方法

注意信号之间的相位关系

CP脉冲从函数信号发生器输出,输出信号为TTL信号,用信号源上SYNC输出端。信号频率用A路单频调节,幅度为固定值5V。

用数字示波器双踪显示,在相应的地址码上观察并记录输入、输出波形,画在坐标纸上,注意其相位关系。

相关文章

发表评论