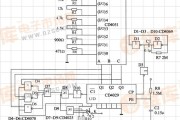

如图1所示是由单八路模拟开关CD4051、可预置可逆计数器CD4029、四导或门CD4070,三3输...

脉冲计数器电路图设计(五) - 脉冲计数器电路图大全(六款脉冲计数器电路设计原理图详解)

脉冲计数器电路图设计(五)

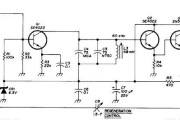

CD4017是5位Johnson计数器,具有10个译码输出端,CP,CR,INH输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。CR为高电平时,计数器清零。Johnson计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。防锁选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应时钟周期内保持高电平。在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。

CD4017逻辑结构图

十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。

CD4017有10个输出端(O0~O9)和1个进位输出端~O5-9。每输入10个计数脉冲,~O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。

CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1~O9)均为低电平。CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。

由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

用CD4017和选择开关组成多进制计数器

CD4017组成的1/n计数器电路图

用CD40171C构成1/n计数器可以分为两种情况:当n=10时,只需使用一块CD4017IC,外接n个门电路即可构成1/n计数器如图1-n所示。在时钟脉冲的作用下,CD4017IC逐个。计数当到第Yn个译码输出时,由外接或非门组成的R-S触发器产生正脉冲输出使CD40171C复零。如果n》=6时,则信号可由进位输出端QCO输出;如果n6时,则信号要由YO译码输出端输出因为n6时,q由端始终保持高电平(参见CD4017波形图),不会产生脉中跳变。

当分频系数n》10时,应根据n的大小来确定CD4017的位数当n=60时的电路工作原理如图1-12所示。输入时钟脉中当个位数的输出YO为“1,十位数的输出Y6为”1“时由外接门电路组成的R-S触发器产生正脉冲输出,从而使各级计数器全部清零。到输入脉冲变为0电平时CD4017的YO输出端又使R-S触发器复位,于是又开始新的一轮计数如此循环往复即得到连续的60分频脉冲输出。

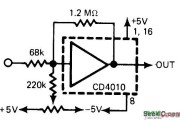

用CD4017组成1~17进制计数器电路

相关文章

发表评论