该图为LatticeECP3设计的视频协议板电路图。 LatticeECP3 FPGA系列能提供高性能的特性如增强的DSP架构,高速SERDE...

低通滤波电路模块设计 - 解读FPGA设计程控滤波器系统电路

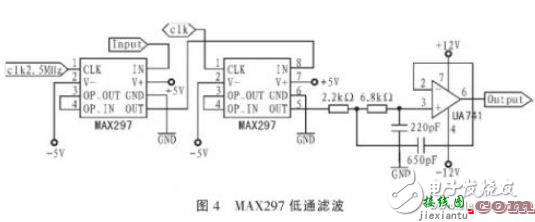

低通滤波模块

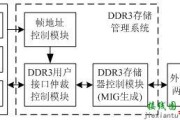

用MAX297 实现低通滤波器。开关电容滤波器MAX297 可以设置为8 阶低通椭圆滤波器,阻带衰减为-80dB,时钟频率与通带频率之比为50:1。通过改变CLK的频率,即可满足滤波器-3 dB 截止频率在1~20kHz 范围内可调,步进1 kHz的要求。

在使用MAX297 时要注意的是,当信号频率和采样辨率同频,开关电容组在电容上各次采到相同的幅度为信号幅值的信号,相当于输入信号为直流的情况,使滤波器输出一个直流电平。同理,当信号频率为采样频率的整数倍时,也会出现相同的现象。为此,在其前面,要增加模拟低通滤波器,把采样频率及其以上的高频信号有效地排除。故又用一级MAX297,截止频率设置为50kHz。其中时钟频率设置为2.5 MHz。在其后面,也要增加低通滤波器,其截止频率为150kHz,以滤去信号的高频分量,使波形更加平滑。具体电路如图4 所示。

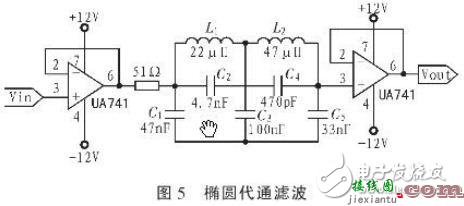

四阶椭圆低通模块

系统要求制作一个四阶椭圆型低通滤波器,带内起伏≤1 dB,-3 dB 通带为50kHz,采用无源LC 椭圆低通滤波器来实现。用Filter Sol ution 模拟仿真滤波器,随后在Multisim 中再模拟仿真并调整电容、电感的参数使其为标称值。此外,在椭圆滤波器前后接射级跟随器避免前后级影岣。具体电路如图5 所示。

本系统放大器增益范围10~60 dB,通频带1~200 kHz,增益误差小于1%。滤波器截止频率范围1~30kHz,误差小于1.5%。椭圆滤波器截止频率误差为0,在150 kHz 处幅度几乎衰减到0。误差主要来源于时钟频率,当截止频率为20 kHz的时候,所需最高的时钟频率为2MHz,不能保证很好的时钟沿,而且时钟频率也不可能精确地控制,以及放大器的非线性误差。此外,利用DAC0800 和有效值检波电路实现了幅频特性测试仪,系统整体性能良好。整个系统在单片机和FPGA 的有机结合、协同控制下,工作稳定,测量精度高,人机交互灵活。

----------------------------------------

以连接器资料集锦——洞悉连接器现状与趋势!

相关文章

发表评论