IGBT(Insulated Gate BipolarTransistor)是绝缘栅双极型晶体管的简称,是一种集功率型场效应管和电力晶体管的优点于一...

VDMOS并联电路设计 - 解读二极管浪涌电流测试电路

接线图

2023年09月27日 21:04 272

admin

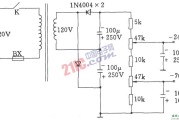

运放组成基本的反向运算电路,驱动VDMOS管的栅极,漏源电流通过VDMOS管源极取样电阻,加到运放反向输入端,与输入波形相加形成反馈,运放输出电压控制VDMOS管的栅极电压VGS,进而控制漏极输出电流IDS[3]。这个IDS就是施加给待测二极管(DUT)的正向浪涌电流。

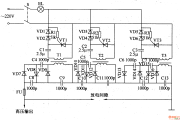

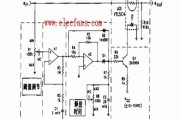

单只VDMOS管的功率和电流放大能力是有限的,无法达到上千安培的输出电流能力,采用多只并联的方式可以解决这个问题,以达到所需要的峰值电流。常见的连接方法如图3所示。

图3 VDMOS并联方式

本测试方案采用了成熟的电路控制技术,简洁而有效地实现了各种浪涌冲击测试的要求。使用的都是常规易得的元器件,组建的装置体积小重量轻,可以很方便地安装在普通仪器箱中,成为一件标准测试仪器。具有使用灵活、易操作,测试精准度高,安全可靠等特点。

----------------------------------------

以太网技术资料集锦——让以太网技术迈向工业物联时代!

相关文章

发表评论