全油门(PWM占空比= 1)当前输出精度完全由R4的精度和LM337内部参考的±2%(保证,通常更好,通常更好)的精度确定。因此,它独立于逻辑供应...

FPGA的EPROM及单片机存储电路设计 - 门禁系统智能视频监控电路设计

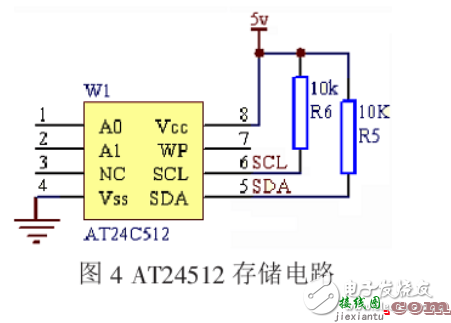

系统中使用了AT24C512EEPROM器件作为主要存储芯片,它的存储容量为512K及单片机对AT24C51系列E2PROM的读写操作完全遵守12C总线的主收从发和主发从收的规则。数据的传送由四部分组成:起始(START)条件、从机地址的发送、数据的传送和停止(STOP)条件。每一个时钟高电平中期间传送一位数据,而且在SCL线为高电平时SDA线上的数据必须保持稳定,否则将认为是一个控制信号。这样设计的优点体现在其简单性和有效性上。

如图4所示电路,一般A0、A1、WP接VCC或GND,SCL、SDA接上拉电阻(上拉电阻的阻值可参考有关数据手册选择,通常可选5K到10K的电阻,本设计中选用的电阻阻值为10K)后再接单片机的普通I/O口,即可实现单片机对AT24C512的操作。在对AT24C512开始操作前,需要先发一个8位的地址字来选择芯片以进行读写。其中要注意“10100”为AT24C512固定的前5位二进制;A0、A1 用于对多个AT24C512加以区分;R/W为读写操作位,为1时表示读操作,为0时表示写操作。AT24C512内部有512页,每一页为128字节,任一单元的地址为

16位,地址范围为0000—0FFFFH。虽然FPGA芯片和单片机都有EEPROM读写的功能,但并不是说它们拥有各自独立的EEPROM芯片,而是两片单片机共同复用EEPROM芯片。如果两个芯片同时读写EEPROM芯片,则单片机肯定会产生死机现象,因此需要一个严格的机制保证不会出现两片单片机同时读或者写EPROM芯片的现象。该机制称为EPROM复用关系,即采用一个握手信号协调两者的使用。

电子发烧友技术编辑点评:在视频选择电路中采用了交流耦合技术,这样设计有利于保持高清晰视频信号的传输。同时利用FPGA作为中央控制部分的,采用了并行的两块单片机做为副控芯片,一块用于USB接口的数据控制与传输,另外一块用于其它接口操作和外部存储控制,既了协调视频信号的实时监控与传输,又能够保证FPGA的处理不受到外部电路的影响,大大提高了系统的工作效率。

相关文章

发表评论