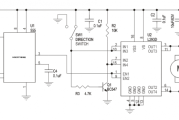

基于 L293D H 桥和 555 定时器 IC 的直流电机速度和方向控制器项目。555 生成 PWM,L293D 作为输出驱动器。293D 提供高达...

采用555时基的抗干扰定时器电路设计

接线图

2023年09月27日 21:06 205

admin

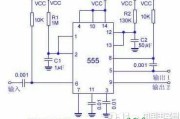

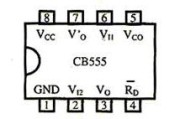

在运用555时基电路设计而成的定时器电路中,一般都将555时基电路连接成单稳态触发器,这样连接使得电路设计简单,只需要几个电阻器和电容器就能实现触发功能,但同时也存在外部对555时基电路2脚的干扰问题,本电路巧妙的利用了555时基电路4脚的强制复位的功能来实现抗干扰的定时器电路。

电路工作原理:在SB断开时,555时基电路的4脚通过电阻器R6与地相连,555时基电路被强制复位。此时,无论2脚受到多大的干扰,555时基电路都不工作。当按下按钮B后,电源通过二极 管VD1加到4脚一个高电平,时基电路的强制复位功能解除,同时电源通过电阻器R1加 到三极管VT1的基极上,使得VT1导通,电容器C2通过与VT1集电极相连后向IC电路的2脚输出一个低电平,IC翻转置位,3脚输出高电平,发光二极管点亮、继电器K得电, 触点K-1闭合,插座对外供电,同时3脚的高电平通过VD2向4脚输出一个高电平使得电路自锁。当暂态结束后,电路翻回稳态,3脚输出低电平,继电器K失电,触头K-1断开,电路恢复到初始状态。

元器件的选择:IC1555时基电路选用NE555、μA555、SL555等时基集成电路;R1~R7选用RTX—1/4W型碳膜电阻器;RP可用WSW型有机实心微调可变电阻器;C2、C4、C5、C6选用CT1型瓷介电容器,C1、C3、C7选用CD11—16V电解电容器;二极管VD1、VD2、VD3选用IN4148硅型开关二极管,VD4~VD7选用IN4001硅型普通整流二极管;继电器K可根据用电设备的需要选择;三端集成稳压器选用7809型三端集成稳压电路。

相关文章

发表评论