这类语音集成电路将语音信号处理后,以数字码形式存储在只读存储器(ROM 中。存储器ROM分为两种:一种是掩膜式ROM,这种ROM在工厂中生产时,已...

揭秘FPGA多重配置硬件电路设计方案

接线图

2023年01月06日 19:09 404

admin

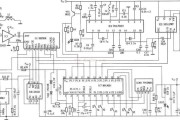

现代硬件设计规模逐渐增大,单个程序功能越来越复杂,当把多个功能复杂的程序集成到一个FPGA 上实现时,由于各个程序的数据通路及所占用的资源可能冲突,使得FPGA 控制模块的结构臃肿,影响了整个系统工作效率。通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH 为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。

当FPGA 完成上电自动加载初始化的比特流后,可以通过触发FPGA 内部的多重启动事件使得FPGA 从外部配置存储器(SPI FLASH)指定的地址自动下载一个新的比特流来重新配置。FPGA 的多重配置可以通过多种方式来实现。

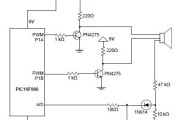

电路原理:

相关文章

发表评论