ADNS-7630 集成了Bluetooth (BT) 2.1的系统级芯片(SoC)LaserStream导航传感器,和 ?Bluetooth H...

CMOS低中频蓝牙射频收发器电路 - 电路图天天读(20):个人局域网电路设计图集锦

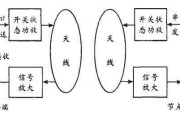

CMOS射频收发器原理:传统的射频收发电路普遍采用超外差结构,这种成熟的体系结构需要采用二级混频和片外声表面滤波器,成本高。正在研发的CMOS低中频或直接转换体系结构只需要采用一级混频,同时能节省片外声表面滤波器。但是直接转换的体系结构需要克服直流失调等问题。采用CMOS射频收发电路的最大优点是可以和基带处理器(数字电路)及A/D、D/A转换器(混合信号电路)集成于一个芯片。单片集成的含射频、基带及模数、数模转换电路使电路可靠性好,功耗低和成本低。单片集成CMOS无线通信电路是目前研究热点,正走上商业化。

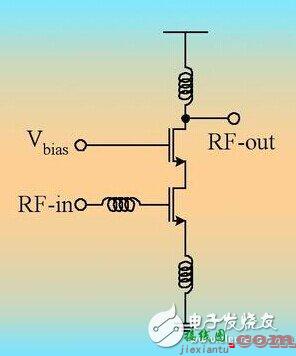

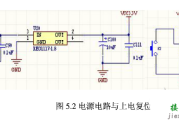

CMOS射频IC电路:采用直接转换的CMOS射频IC主要有低噪声放大器、混频电路、功率驱动电路和频率综合电路等射频单元组成。在射频领域,我们更多注意的是功率传输和放大,其中低噪声放大器的电路图如图所示。

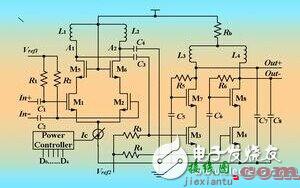

它的核心技术是输入阻抗匹配和输出负载的设计,片上电感作为负载可以获得较高的增益和频率特性,为了抑制共模电平,差分结构的低噪声放大器也经常采用。国内已有CMOS混频器报导采用吉尔布特乘法单元的混频电路如图3所示,混频器的性能主要是线性度,在提高线性度方面,目前有人采用电感负载和共源极电流耦合输入。功率驱动电路一般会采用二级功率放大的电路,为了满足不同射频系统的需要和保证输出功率,功率驱动电路需要考虑增益控制电路和封装、连线及引脚的分布参数。为了得到低噪声时钟和低相位噪声的正交信号,采用片上电感和变容二极管的LC信频压控器及二分频正交信号产生器是一种好的选择。

采用倍频VCO可以减少射频信号对VCO的牵引和VCO对信号的泄漏。Sigma-Delta分数分频能够进一步降低VCO的相位噪声。低中频(2MHz中心频率)体系结构和直接转换的蓝牙、无线局域网和WCDMA射频电路。图6是单片集成的CMOS射频收发电路芯片照片,芯片左上角是正交时钟产生电路,右下角是功率放大电路,右上角是复数滤波器。在深亚微米CMOS工艺线流片后,对各功能块进行测试,电路达到了设计的要求,能够满足蓝牙接收芯片必须的功耗和性能。

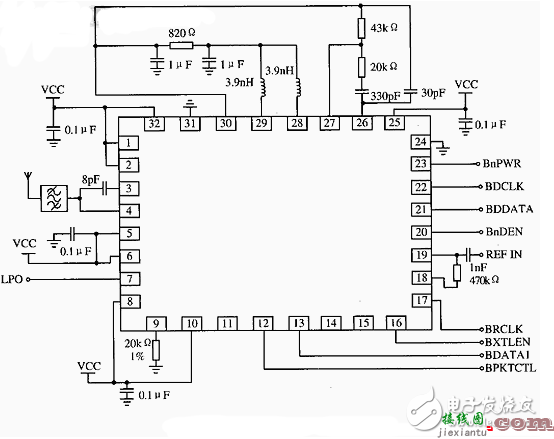

TOP11 蓝牙无线局域网收发芯片RF2968接口电路

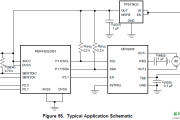

接口电路原理:RF2968 发射机输出在内部匹配到50Ω,需要1个AC耦合电容。接收机的低噪声放大器输入在内部匹配50Ω阻抗到前端滤波器。接收机和发射机在TXOUT和 RXIN间连接1个耦合电容,共用1个前端滤波器。此外,发射通道可以通过外部的放大器放大到+20dBm,接通RF2968的发射增益控制和接收信号强度指示,可使蓝牙工作在功率等级一。RSSI数据经串联端口输入,超过-20~80dBm的功率范围时提供1dB的分辨率。发射增益控制在 4dB步阶内调制,可经串联端口设置。基带数据经BDATA1脚送到发射机。BDATA1脚是双向传输引脚,在发射模式作为输入端,接收模式作为输出端。 RF2968实现基带数据的高斯滤波、FSK调制中频电流控制的晶体振荡器(ICO)和中频IF上变频到RF信道频率。片内压控振荡器(VCO)产生的频率为本振(LO)频率的一半,再通过倍频到精确的本振频率。在RESNTR+和RESNTR-间的2个外部回路电感设置VCO的调节范围,电压从片内调节器输给VCO,调节器通过1个滤波网络连接在2个回路电感的中间。由于蓝牙快速跳频的需要,环路滤波器(连接到 DO和RSHUNT)特别重要,它们决定VCO的跳变和设置时间。所以,极力推荐使用电路图中提供的元件值。RF2968可以使用10MHz、 11MHz、12MHz、13MHz或20MHz的基准时钟频率,并能支持这些频率的2倍基准时钟。时钟可由外部基准时钟通过隔直电容直接送到OSC1 脚。如果没有外部基准时钟,可以用晶振和2个电容组成基准振荡电路。无论是外部或内部产生的基准频率,使用1个连接在OSC1和OSC2之间的电阻来提供合适的偏置。基准频率的频率公差须为20×10-6或更好,以保证最大允许的系统频率偏差保持在RF2968的解调带宽之内。LPO脚用3.2kHz或 32kHz的低功率方式时钟给休眠模式下的基带设备提供低频时钟。考虑到最小的休眠模式功率消耗,并灵活选择基准时钟频率,可选用12MHz的基准时钟。

接收机用低中频结构,使得外部元件最少。RF信号向下变频到1MHz,使中频滤波器可以植入到芯片中。解调数据在BDATA1脚输出,进一步的数据处理用基带PLL数据和时钟恢复电容完成。D1是基带PLL环路滤波器的连接脚。同步数据和时钟在REDATA和RECCLK脚输出。如果基带设备用 RF2968做时钟恢复,D1环路滤波器可以略去不用。

相关文章

发表评论