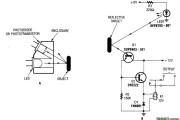

心电图机前置放大电路光隔离器可防止循环接地电流在试验时电击患者。在医疗环境中,几乎可与所有类型的AC线供电设备一起使用。 ...

电路描述 - 通用串行总线(USB)集线器隔离器电路图

电路描述

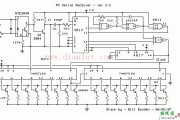

上游USB连接器所用的电源从USB电缆提供的5 V VBUS电压获得。集线器芯片必须提供未使用ADuM4160时所需要的所有信号和上拉/下拉电阻。所选的集线器芯片为 SMSC USB2512双端口USB集线器控制器,它具有低成本和小尺寸的特点。此外,还可以使用相同尺寸的4通道版本。本设计为全功能型,通过MIC2026配电开关支持各通道的限流功能,并具有充足的离线稳压电源,可为下游各通道提供2.5 W功率。下游侧的电源由一个壁式电源适配器和ADP3339 LDO调节器(5 V选项)提供。此器件可提供非常低的压差,从而降低了对壁式电源适配器的调节要求。其小尺寸特点和1.5 A电流能力非常适合这种通用电路,其下游外设可能需要电缆的全部功率才能工作。

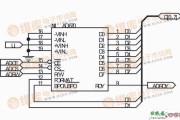

ADuM4160具有多种电源、速度和保护选项,必须加以确定。外设以三种速度之一运行:低速(1.5 Mbps)、全速(12 Mbps)和高速(480 Mbps)。ADuM4160不支持高速运行,会阻止用于协商该速度的握手信号。所选的集线器芯片支持高速运行,但ADuM4160的正常运行不允许这种模式。必须通过SPU和SPD引脚的状态将ADuM4160设置为以全速工作。在目前的原理图中,SPU和SPD引脚连接到3.3 V稳压电源VDD1和VDD2,从而将器件设置为全速运行。

可以通过VBUSx引脚提供5 V电源。3.3 V信号电压由内部3.3 V调节器在VDDx引脚产生。另一种选择是直接向VBUSx和VDDx提供3.3 V电源。器件能够检测到这种配置,并直接使用3.3 V电源,禁用内部调节器。出于说明需要,ADuM4160配置为接受一个3.3 V外部电源,并且旁路内部调节器。VBUS2和VDD2引脚短路连在一起,由ADP3330 LDO调节器产生的3.3 V外部电压供电。

ADuM4160还提供一个选项,可以在外设控制下延迟应用上游上拉电阻。此功能由PIN输入控制。在本应用中,PIN输入短路至高电平,因此,只要对集线器芯片施加电源,就会用到上游上拉电阻。在有些应用中,可以将它连接到一个控制器的GPIO引脚,可以采用一个固定延迟电路,或者可以像本电路一样连接。如何使用此功能取决于设计人员。

本电路还显示了EOS/ESD保护器件。这些器件选自那些提供各种不同器件的制造商,所选的特定器件允许用0 Ω短路电阻予以代替,以便将其从电路中移除。设计人员应当仔细考虑保护器件选择,包括不需要外部保护到需要全套瞬变抑制器和滤波器元件的各种情况。本应用电路所包括的元件是可以使用的典型元件。

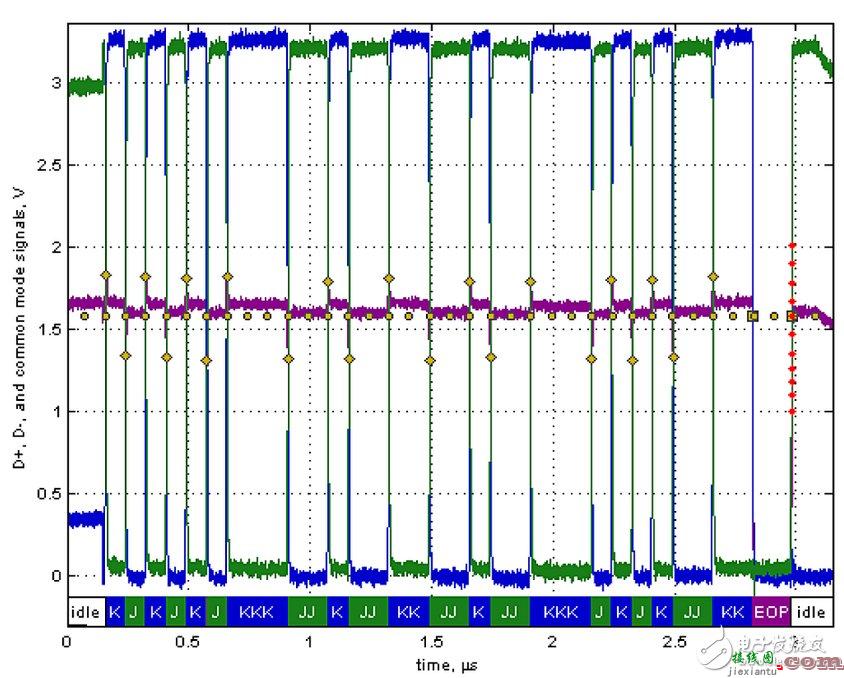

当电路工作时,会进行包检测,并将数据从隔离的一侧传送到另一侧。图2和图3所示的数据分别以时域数据和眼图形式展示了典型的全速处理情况。

图2. ADuM4160上游端口驱动的全速测试包流量

在实时数据中,需要注意的特点是包开始时为无源空闲状态,它会转换为受驱J状态,还有处理结束时的包末尾显示为单端0状态,其后是空闲J状态。正是这种自动控制流和对这些特殊逻辑状态的处理,才使ADuM4160芯片得以实现,并且是市场上独一无二的。

该集线器设计与上游数据连接完全隔离,可承受最高达5 kV的瞬变电压。下游端口通过离线电源供电,以支持全功率应用。低速、全速和高速外设可以任意组合连接到下游端口,集线器控制器根据USB标准正确协商速度。此设计中还包括电流切换和限制功能,还为其它输出保护器件预留了位置,设计人员可以根据需要选择安装。

以下所列为适用的测试参考文件:

上游全速信号质量测试参考文件—USB 2.0规范第7.1.11节、第7.1.2.1节

上游全速上升时间测试参考文件—USB 2.0规范第7.1.11节、第7.1.2.2节

上游全速下降时间测试参考文件—USB 2.0规范第7.1.11节、第7.1.2.2节

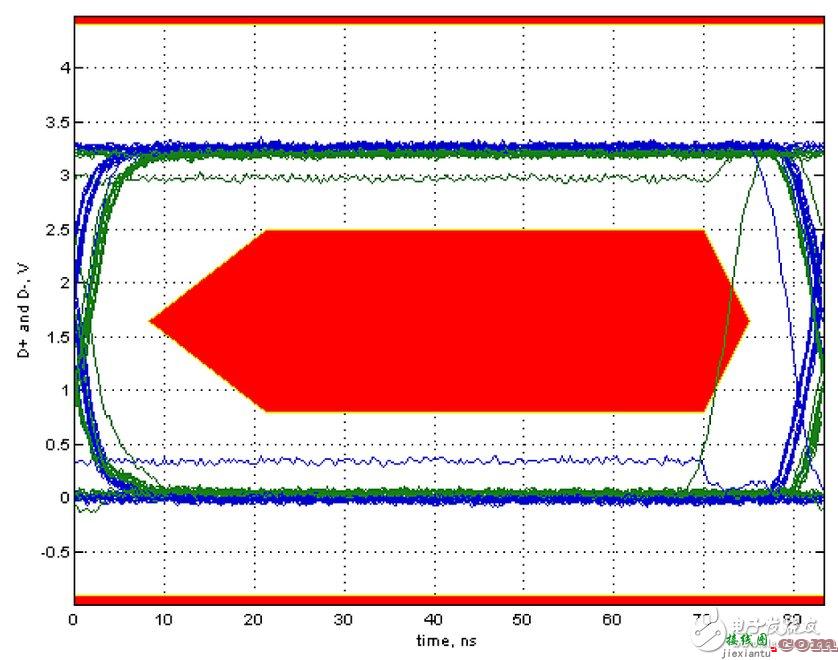

图3为全速眼图,显示ADuM4160能够提供充分张开的眼图,并远离禁入区域。但有一个转换是例外,它侵入了禁入区。对于这种测试认证来说这是可以接受的。针对低速评估也获得了类似的数据。评估板的照片如图4所示。欲了解布局文件,请访问: www.analog.com/CN0158_Board_Layout.

图3. 显示禁入区域的全速眼图

图4. ADuM4160隔离USB集线器评估板

相关文章

发表评论