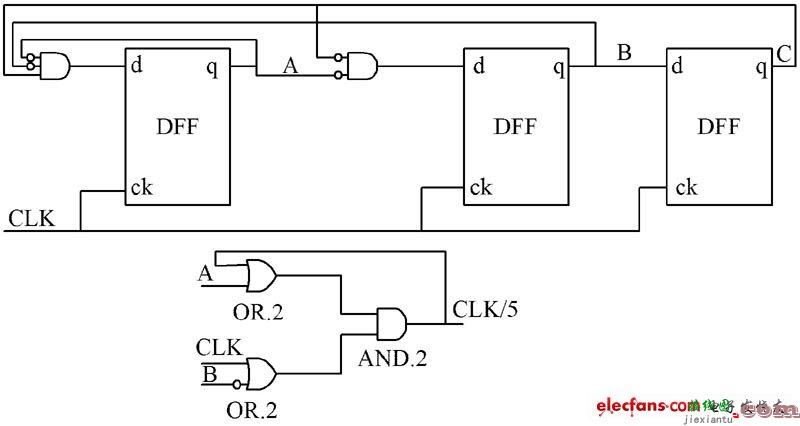

D触发器结构的五分频器逻辑电路由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时钟信号CLK, A 和B 进行逻辑运算得到占空比为50% 的五分频信号CLK/ 5, 其计数过程如表1 所示, 从表1 的计数过程可知, 分频后的时钟CLK/ 5 的周期是输入时钟CLK 的5 倍, 由此实现了五分频并且其占空比为50% .

版权与免责声明

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

发表评论