电路说明:CMOS电路直接驱动来自两个缓冲输出的任何一个的5 TTL负荷。该电路的工作频率是10MHz,是一个与CMOS兼容的两极场效应管。 ...

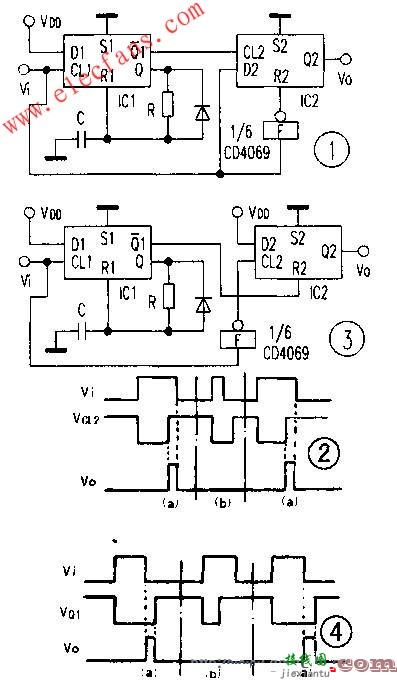

基于CMOS双D触发器CD4013的脉冲宽度检测电路设计

D触发器的常规使用一般是用作二分频器、计数器或移位寄存器。然而,只要对D触发器的外围电路加以改进,根据其基本逻辑功能。就可充分发挥其独特的作用。数字装置中常用的脉冲宽度检测电路,对脉冲信号的宽度进行识别,例如,当输入脉冲的宽度为一个特定值时。便产生一个响应,否则就不予响应。以下就用CMOS双D触发器CD4013组成的几种脉冲宽度检测电路作一介绍。

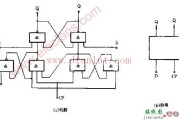

检测线路之一如图l所示。ICl、IC2为一片CD4013,其中ICl构成一单稳态触发器,单稳态输出端Q1作为D触发器IC2的时钟脉冲,Q2端作vo输出端。由于ICl、IC2的置位S端接地,故稳态时ICl的Ql端恒为零,Ql端为高电平,VO输出为低电平。当Vi输入信号为高电平时,将Dl端的高电平送入ICl触发器,Ql端跳变为高电平,Ql端为低电平,暂稳态开始,IC2触发器不触发,VO仍为低电平。当Vi下眺时,ICl单稳电路的暂稳态还未结束(见图2b所示),IC2触发器仍未触发,VO为低电平。待ICl的暂稳态结束,ICI触发器复位,Ql端为低电平,Ql端上眺为高电平。尽管IC2的CL2端上眺。但由于此时Vi输入信号已为低电平,经反相器F反相使IC2的复位端R2为高电平,故VO端仍为低电平。

另一种情况是:当Vi为高电平,Ql端为低电平时,ICl暂稳态开始,VO为低电平。当ICl的暂稳态结束时,Vi仍为高电平(见图2a所示),Ql端上跳,IC2触发翻转,R2端处于低电平,D2端的高电平送入IC2,VO端输出高电平。当Vi下跳时,经F使IC2的R2端为高电平,迫使IC2复位。VO输出为低电平。

由此可见,只有当Vi输入信号脉冲宽度大干ICl的单稳态输出脉宽时。IC2触发器才有输出。

检测线路之二如图3所示。该线路和图1相似,不同的是Vi输入信号经反相器F反相后作为IC2的CL2时钟脉冲。ICl仍为一单稳电路。稳态时,V0为低电平。当Vi为高电平时,Ql端为高电平,暂稳态开始,IC2未触发,V0为低电平。当ICl单稳态结束时(见图4b所示),Ql端回复到低电平,此时Vi仍为高电平,故VO为低电平。当Vi下跳时,经F反相使。IC2的LC2端上跳,但由于Ql端即ZC2的R2端为高电平,所以VO仍为低电平。

另一种情况是:当Vi为高电平时,Ql为高电平,ICl暂稳态开台,IC2未触发,V0为低电平。当Vi下眺时,暂稳态未结束,Q1端仍为低电平,IC2触发翻转,VO输出高电平(见图4a)。当ICl单稳态电路暂稳态结束时,Ql端上跳为高电平,迫使IC2复位,VO输出为低电平。由此可见,只有当Vi输入信号脉宽小于ICl的单稳态输出脉宽时。IC2触发器才有输出。

相关文章

发表评论