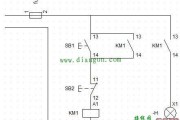

在开始编程时,我们先了解下后面要经常用到的梯形图编程语言。先看下面的一个自锁继电器电路图:SB1按下,继电器KM1得电,相应的常开点KM1就会闭合,灯...

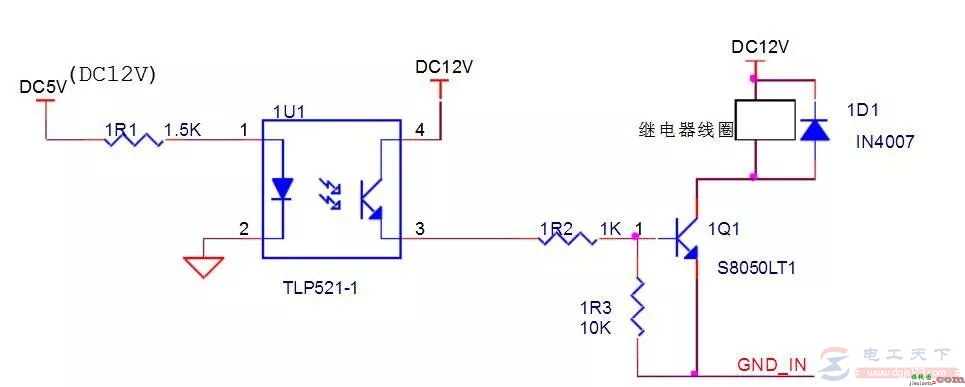

光耦驱动继电器电路图及功能说明

接线图

2022年12月31日 19:16 369

admin

说明:

1U1-1脚可接12V,也可接5V,1U1导通,1Q1导通,1Q1-3=0V,线圈两端电压为11.7V。

1U1-1脚不接或接地,1U1不通,1Q1截止,1Q1-3=11.9V,线圈两端电压为0V。

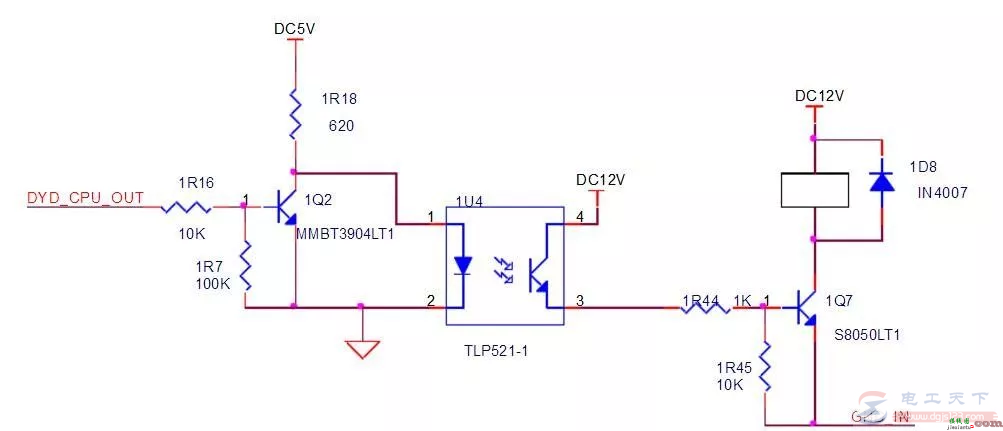

说明:

“DYD_CPU_OUT”连接LPC2367,输出高低电平,高电平,1U4不通,1Q7不通,UCE=12V,1Q7-3=12V,线圈两端电压为0V。

DYD_CPU_OUT”为低电平,1U4导通,U43=1V,U3=11V,UCE=0V,1Q1-3=0V,线圈两端电压为11.7V。以上两图为低电平使能。

以上二种适用于CPU初始化时,GPIO口为高电平的情况,否则初始化会造成误动作。

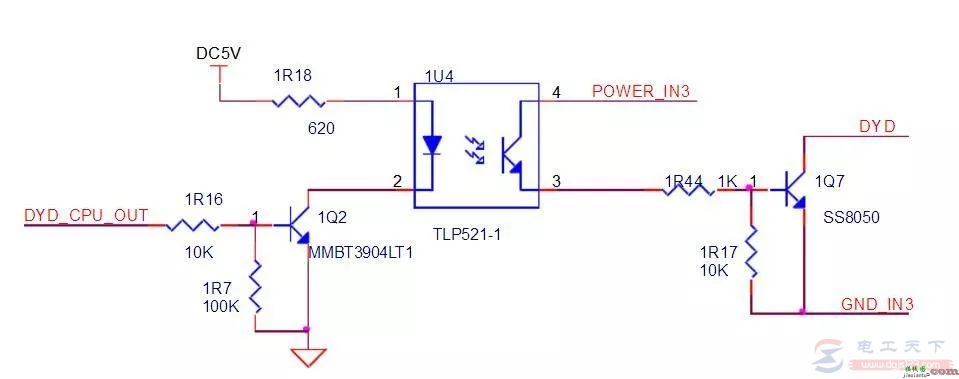

“DYD_CPU_OUT”连接LPC2367,输出高低电平,低电平,1U4不通,1Q7不通,UCE=12V,1Q7-3=12V,线圈两端电压为0V。

“DYD_CPU_OUT”为高电平,1U4导通,U43=1V,U3=11V,UCE=0V,1Q1-3=0V,线圈两端电压为11.7V。此图为高电平使能,继电器的常闭触点接负载。

第2和第3图中的1R16换成510欧,1R7换成1K,以防止有上电瞬间,高电平干扰。尤其是第3图,高电平使能。

相关文章

发表评论