该图为LatticeECP3设计的视频协议板电路图。 LatticeECP3 FPGA系列能提供高性能的特性如增强的DSP架构,高速SERDE...

基于Verilog的FPGA与USB 2.0高速接口设计

0 引 言

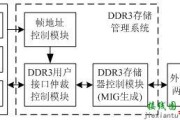

在高速的数据采集或传输中,目前使用较多的都是采用USB 2.0接口控制器和FPGA或DSP实现的,本设计在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作为外部主控制器实现对FX2 USB内部的FIFO进行控制,以实现数据的高速传输。该模块可普遍适用于基于USB 2.0接口的高速数据传输或采集中。

l 系统硬件模块设计

1.1 系统硬件框图

图1中展示了Slave FIFO方式下FX2 USB和FPGA的典型连接。其中,FD[7..O]为8位双向数据总线FLAGA~FLAGC为FX2内FIFO的标志管脚,映射FIFO的当前状态;SLCS为Slave FIFO的片选信号;SLOE用于使能数据总线FD的输出;FIFOADR[1..0]用于选择和FD连接的端点缓冲区(00代表端点2,01代表端点 4,10代表端点6,11代表端点8);SLRD和SLWR可分别作为FIFO的读写选通信号。

1.2 USB 2.0接口芯片CY7C68013

1.2.1 CY7C68013的结构特点

Cypress公司的USB FX2是第一个包含USB 2.0的集成微控制器,它内部集成了1个增强型的8051,1个智能USB串行接口引擎,1个USB数据收发器,3个8位I/O口,16位地址线,8.5 KB RAM和4 KBFIFO等。增强性8051内核完全与标准8051兼容,而性能可达到标准8051的3倍以上。其框图如图2所示。

1.2.2 CY7C68013的工作模式

CY7C68013有Ports模式、Slave FIFO和GPIF三种接口方式。

Ports模式是一种最基本的数据传输方式,其数据传输主要由固件程序完成,需要CPU的参与,因此数据传输速率比较低,适用于传输速率要求不高的场合。

Slave FIFO方式是从机方式,外部控制器,如FPGA,可像对普通FIFO一样对FX2的多层缓冲FIFO进行读写。FX2内部的FIFO提供所需的时序信号、握手信号(满、空等)和输出使能等。这里就是在Slave FIFO模式下实现USB 2.O接口和FPGA的数据通信。

可编程接口GPIF是主机方式,GPIF作为内部主机控制端点FIFO,可以软件编程读写控制波形,几乎可以对任何8/16 b接口的控制器、存储器和总线进行数据的主动读写,非常灵活。

2 系统软件模块设计

2.1 USB固件程序设计

应用中采用异步FIFO方式,使用内部48 MHz时钟,自动方式,固件程序采用Cypress公司提供的固件程序框架,在其初始化函数中添加了用户配置代码。该设计中异步自动从属FIFO数据传输的初始化代码如下:

2.2 FPGA控制程序设计

CY7C68013A提供的端口FIFO的读写操作,与普通FIFO读写操作方式一样。CY7C68013A为每个端口提供了“空”标志、“满”标志和“ 可编程级”标志。FPGA检测这些信号,用于控制读写的过程。FPGA在完成这些端口FIFO的操作时,采用VerilogHDL硬件描述语言实现了FIFO的读写时序,并在ALTERA公司提供的QuaRTUsⅡ8.O开发工具中综合编译并映射到FPGA中运行。

2.2.1 从属FIFO异步“读”操作

实现异步从属FIFO“读”的状态机如图3所示。其状态转移进程如下:

IDLE:当“写”事件发生时,转到状态1。

状态1:指向OUT FIFO,激活FIFOADR[1:O],转向状态2。

状态2:激活SLOE,如果FIFO空标志为“假”(FIFO不空),则转向状态3;否则停留在状态2。

状态3:激活SLOE,SLRD,传送总线采样数据;撤销激活SLRD(指针加1)和SLOE,转向状态4。

状态4:如果有更多的数据要求,则转向状态2;否则转向IDLE。

实现以上状态机的仿真波形如图4所示。

2.2.2 从属FIFO异步“写”操作

实现异步从属FIFO“写”的状态机如图5所示。其状态转移进程如下:

IDLE:当写事件发生时,转到状态1。

状态1:指向IN FIFO,激活FIFOADR[1:O],转向状态2。

状态2:如果FIFO满标志为“假”(FIFO不满),则转向状态3;否则停留在状态2。

状态3:传送总线驱动数据。为一个IFCLK激活SLWR,转向状态4。

状态4:如果有更多的数据要写,则转向状态2;否则转向IDLE。

用QuartusⅡ进行仿真验证,其仿真波形如图6所示,在此过程中USB_SLWR信号很重要,经分析可知,本状态机实现的FIFO写控制信号完全正确。

3 实验结果

对传输的数据进行验证,可通过FPGA编程生成O~255的数据传送至CY7C68013的EP6端点,连续传送两次,然后利用EZ一USB Control Panel软件测试所接收到的数据,测试结果如图7所示,可以看出,数据传输准确无误。

4 结 语

USB 2.0控制器CY7C68013已经被广泛应用到许多数据传输领域,由于USB具有灵活的接口和可编程特性,大大简化了外部硬件的设计,提高了系统可靠性。该设计可扩展性好,已经被应用于数据传输与采集的板卡上,经实际测试,没有出现数据的误码等错误,数据传送正确,传输速率可达30 MHz/s以上,满足设计要求。

标签: fpga Verilog USB 高速接口 QUARTUS

相关文章

发表评论