这是Intel 820e主板处理器连接器电路图。 ...

音频编码连接器应用电路设计攻略 —电路图天天读(98)

介绍一下音频处理模块,ADSP-21369具有很强的音频处理能力,使用音频编码解码器AD1835A进行音频信号的处理,先简单叙述一下整个音频模块输入模拟音频信号,并输出模拟音频信号的处理过程,模拟音频信号从接头ADC输入,经过处理后供给AD1835A的 ADC输入ADCLN,ADCLP,ADCRN和ADCRP,然后在AD1835A内进行AD转换,并将转换后的数据由AD1835A的串口数据输出ASDATA交给DSP处理,经过DSP处理后的数据再通过AD1835A的DAC数据输入 DSDATA1,DSDATA2,DSDATA3,DSDATA4进行DA转换,最后通过AD1835A的DAC输出 OUTRP4,OUTRN4,OUTLP4,OUTLN4,并将其经过滤波电路处理给音频的线路输出DAC4和耳机输出DACHEAD。

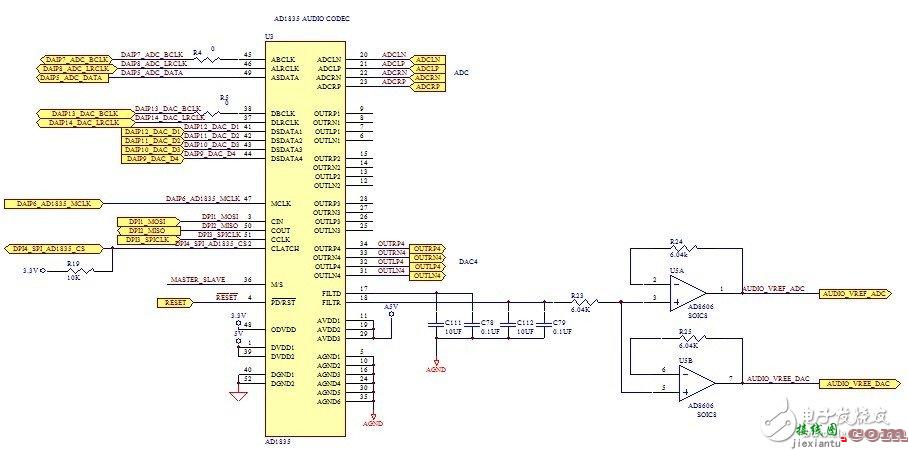

DSP处理器和AD1835A芯片的连接电路

DSP处理器通过DAI接口和AD1835A芯片相连。音频芯片的内部配置寄存器是通过处理器的SPI口来完成的。DPI4引脚被用来做为设备的片选,DAI引脚可以被配置成以时分复用(TDM)模式或者2线接口模式(TWI)从AD1835A传输串行数据。此外,我们只设计用到一路DAC4音频输出。如图1所示。

图1 AD1835A和DSP的连接电路图

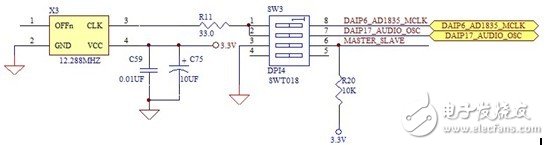

AD1835A时钟电路

AD1835A的主输入时钟(MCLK)可以由板上12.288Mhz的晶振产生,或者由DSP处理器上的DAI引脚提供,并通过开关SW3的1,2引脚位置配置。用DAI引脚产生晶振,允许多重器件同步,例如当数据来自索尼飞利浦数字接口(S/PDIF)接收器的时候,可以通过音频芯片输出。此时,S /PDIF的MCLK来自于AD1835A的MCLK。

开关的第三个位置决定了主从模式的选择。当开关的3和6相连时,即开关闭合的状态,MASTER_SLAVE为低,主模式,AD1835的串行接口来提供帧同步和时钟信号;3和6断开时,即开关关闭的状态,MASTER_SLAVE为高,从模式,DSP处理器需要提供帧同步和时钟信号,默认开关为闭合状态。

图2 AD1835A时钟电路图

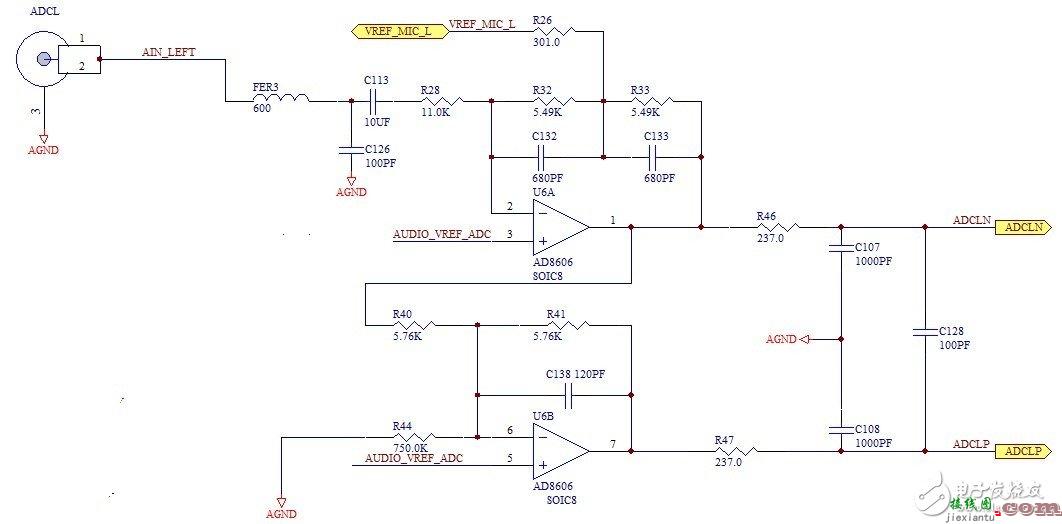

ADC输入电路

ADC输入电路部分,主要采用AD8606搭建成T型滤波电路,前端电路是音频信号输入,后端是经过处理的平衡输出音频信号,AD8606是双路轨到轨输入和输出、单电源放大器,具有极低失调电压、低输入电压和电流噪声以及宽信号带宽等特性。由于AD8606是单电源,因此要提供参考电压 AUDIO_VREF_ADC使两端平衡输出ADCLN和ADCLP都以参考电压为中心,我们使用RCA接口ADCL和ADCR被用来输入模拟信号,左声道ADC输入电路如图3所示,右声道电路和此部分电路相近。

图3 ADC输入电路图

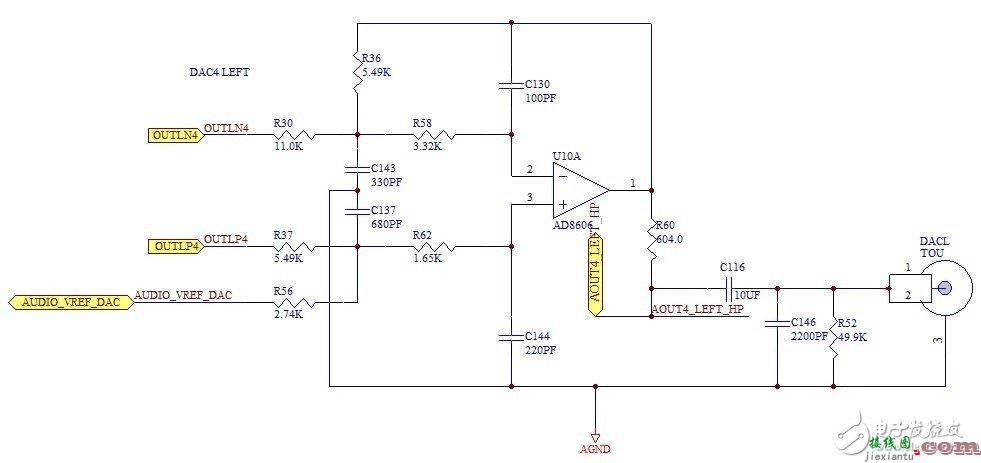

DAC输出电路

考虑到DAC音频输出包括线路输出和耳机输出,并且国际上有个标准,要求线路输出阻抗最好是一定的数值,以便和功放、有源音箱、耳放的输入阻抗相配,因为这样的声音失真最小并且音质最好,而耳机的阻抗一般是几十或几百欧姆,耳机所需要的电流、电压也比功放、有源音箱、耳放所需要的大,因为需要足够的电压和电流把它推动起来,就需要输出设备有较小的输出阻抗,较大的输出电压、电流和它配合。所以需要两个接口,两个不同的电路,使输出满足各自不同要求的电路指标。DAC线路输出采用AD8606搭建成低通平滑滤波电路,同样的,由于AD8606是单电源,因此要提供参考电压AUDIO_VREF_DAC使两端平衡输出ADCLN和ADCLP都以参考电压为中心,DAC左声道输出电路如图4所示,右声道输出电路和此类似,详见附录。输出通道和RCA接口DACL 和DACR相连。

图4 DAC输出电路图

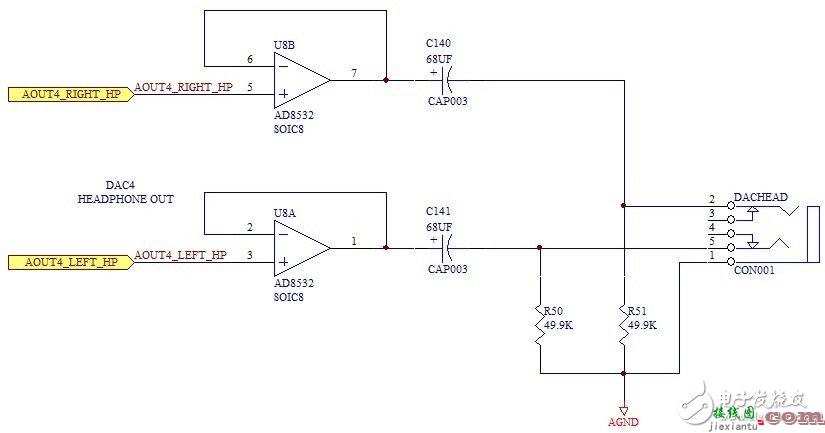

耳机输出电路通过AD8532搭建成同相跟随器电路,AD8532是单电源低功耗双路轨到轨输入和输出放大器,输出电流为250mA,如图5所示。音频芯片的通道4和耳机接口DACHEAD相连。

图5 DAC耳机输出电路图

电子发烧友网技术编辑点评分析:

根据编码方式的不同,音频编码技术分为三种:波形编码、参数编码和混合编码。一般来说,波形编码的话音质量高,但编码速率也很高;参数编码的编码速率很低,产生的合成语音的音质不高;混合编码使用参数编码技术和波形编码技术,编码速率和音质介于它们之间。

大家如有问题,欢迎在评论处讨论。

——电子发烧友网整理,转载请注明出处!

----------------------------------------

以太网技术资料集锦——让以太网技术迈向工业物联时代!

相关文章

发表评论