该电路图中展示了 Microchip 技术推出的一个非常有趣的喇叭驱动器项目。该喇叭驱动器项目基于 Microchip 的 PIC16F886 微控制...

FPGA电子电路设计图集锦TOP12 —电路图天天读(105)

现场可编程门阵列即FPGA,是从EPLD、PAL、GAL等这些可编程器件的基础上进一步发展起来的。作为专业集成电路领域中的半定制电路而出现的FPGA,不但解决了定制电路的不足,而且克服了原有可编程器件因门电路数有限的而产生的缺点。FPGA 的使用十分的灵活,同一片FPGA 只要使用不同的程序就能够达到不同的电路功能。现在FPGA 在通信、仪器、网络、数据处理、工业控制、军事和航空航天等众多领域有着广泛的应用。随着成本和功耗的进一步降低,将在更多的领域运用FPGA。

TOP1 解读FPGA程控滤波器系统电路

滤波器是一种用来消除干扰杂讯的器件,可用于对特定频率的频点或该频点以外的频率进行有效滤除。它在电子领域中占有很重要的地位,在信号处理、抗干扰处理、电力系统、抗混叠处理中都得到了广泛的应用。而对于程控滤波器,该系统的最大特点在于其滤波模式可以程控选择,且-3 dB 截止频率程控可调,相当于一个集多功能于一体的滤波器,将有更好的应用前景。此外,系统具有幅频特性测试的功能,并通过示波器显示频谱特性,可直观地反应滤波效果。

放大模块

放大模块的具体电路如图2 所示。第一部分是一个分压网络,其中前4 个电阻将输入信号衰减100 倍,并与信号源内阻共同构成51Ω阻抗,后面的51Ω为匹配电阻。第二部分采用OPA690 将小信号放大2 倍,同时起到阻抗变换和隔离的作用。由于AD603 输入阻抗为100Ω,所以在后面串接一个100 Ω的电阻进行匹配。第三部分即为AD603 可变增益放大,它的增益随着控制电压的增大以dB为单位线性增长。1 脚的参考电压通过单片机进行运算并控制DAC 芯片输出电压来得到,从而实现精确的数控。增益G(dB)=40VG+G0,其中VG 为差分输入电压,范围-500~500mV;G0 是增益起点, 接不同反馈网络时也不同。在5、7 脚间接一个5kΩ的电位器,从而改变。

高通滤波模块

LTC1068 是低噪声高精度通用滤波器,当其用于高通滤波时,截止频率范围1Hz~50 kHz,并且直至截止频率的200 倍都无混叠现象。由于LTC1068 的4 个通道都是低噪声、高精度、高性能的2 阶滤波器,因此每个通道只要外接若干电阻就可以实现低通、高通、带通和带阻滤波器的功能。具体电路如图3 所示。其中B 端口Q 值0.57,A 端口Q 值约为1。在电路的调试中发现,A 口的Q值需比B 口Q 值大,否则信号在截止频率处幅值会有上翘。

LTC1068 的时钟频率与通带之比为200:1,由于LTC1068 内部对时钟信号CLK二倍频,所以当截止频率最小为1 kHz 时,内部时钟频率其实为400kHz,故在LTC1068 后面再加一个截止频率为450kHz 的低通滤波器以滤除分频带来的噪声及高次谐波。

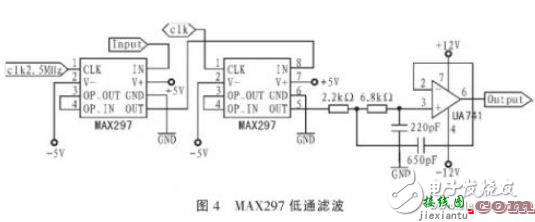

低通滤波模块

用MAX297 实现低通滤波器。开关电容滤波器MAX297 可以设置为8 阶低通椭圆滤波器,阻带衰减为-80dB,时钟频率与通带频率之比为50:1。通过改变CLK的频率,即可满足滤波器-3 dB 截止频率在1~20kHz 范围内可调,步进1 kHz的要求。

在使用MAX297 时要注意的是,当信号频率和采样辨率同频,开关电容组在电容上各次采到相同的幅度为信号幅值的信号,相当于输入信号为直流的情况,使滤波器输出一个直流电平。同理,当信号频率为采样频率的整数倍时,也会出现相同的现象。为此,在其前面,要增加模拟低通滤波器,把采样频率及其以上的高频信号有效地排除。故又用一级MAX297,截止频率设置为50kHz。其中时钟频率设置为2.5 MHz。在其后面,也要增加低通滤波器,其截止频率为150kHz,以滤去信号的高频分量,使波形更加平滑。具体电路如图4 所示。

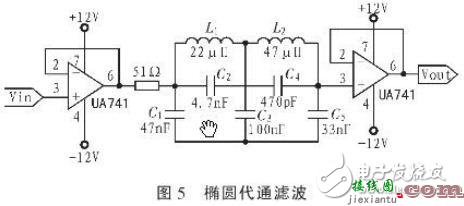

四阶椭圆低通模块

系统要求制作一个四阶椭圆型低通滤波器,带内起伏≤1 dB,-3 dB 通带为50kHz,采用无源LC 椭圆低通滤波器来实现。用Filter Sol uTIon 模拟仿真滤波器,随后在MulTIsim 中再模拟仿真并调整电容、电感的参数使其为标称值。此外,在椭圆滤波器前后接射级跟随器避免前后级影岣。具体电路如图5 所示。

----------------------------------------

FPGA资料集锦——那些年,我们为之癫狂的FPGA设计

TOP2 FPGA电源定序电路原理分析

图1 这种电源定序电路可消除闭锁问题,并可减少FPGA 起动瞬态电流。

电路原理:图 1 所示电源包含IC1 和IC2 两块IC,它们分别是TPS2034 电源开关和TPS54680降压型开关稳压器。IC1 产生IC2 在起动期间跟踪的慢斜坡电压。6ms 的斜坡时间可使加到电源开关大电容和电源输出端的涌入电流降到最小值。慢斜坡电压能使FPGA 吸收的瞬态电流最小。电源开关TPS2034 确保在IC2 具有足够大的偏置电压运作并产生芯核电压之前,I/O 电压不会加到负载上。假如J1 的输入电压为3.3V,则J2 连接器上的电压浮动就会使IC1 起动。I/O 电源电压J3 就慢慢上升,直到达到3.3V 为止。由于I/O 电压上升,芯核的电源电压相应升高,直到1.8V 为止(图2)。TPS54680 的TRACKIN 引脚内包含有一个模拟多路转换器,以便实现跟踪功能。P 在加电和断电期间,当TRACKIN 引脚上的电压低于0.891V 内部基准电压时,TRACKIN 引脚上的电压就连接到误差放大器的非倒相节点。当TRACKIN 引脚电压低于0.891V 时,该引脚就能有效地起开关稳压器的基准作用。连接TRACKIN 引脚的R3 和R4 电阻分压器必须等于反馈补偿回路中的R1 和R2 分压器,才能在加电和断电期间以最小的电压差进行跟踪。TPS2034 具有37mΩ的导通电阻,并能提供2A 那么大的输出电流。

揭秘FPGA多重配置硬件电路设计方案

现代硬件设计规模逐渐增大,单个程序功能越来越复杂,当把多个功能复杂的程序集成到一个FPGA 上实现时,由于各个程序的数据通路及所占用的资源可能冲突,使得FPGA 控制模块的结构臃肿,影响了整个系统工作效率。通过FPGA 的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA 器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH 为基础,从硬件电路和软件设计两个方面对多重配置进行分析,给出了多重配置实现的具体步骤,对实现复杂硬件设计工程有一定的参考价值。

电路原理:多重配置的硬件主要包括FPGA 板卡和贮存配置文件的FLASH 芯片。FPGA 选用XILINX 公司Virtex-5系列中的ML507,该产品针对FPGA 多重配置增加了专用的内部加载逻辑。FLASH 芯片选用XILINX 公司的SPI FLASH芯片M25P32,该芯片存贮空间为32 Mb,存贮文件的数量与文件大小以及所使用的FPGA 芯片有关。实现多重配置首先要将FPGA 和外部配置存储器连接为从SPI FLASH 加载配置文件的模式。配置电路硬件连接框图如图1所示。在FPGA 配置模式中,M2,M1,M0为0,0,1,这种配置模式对应边界扫描加上拉,FPGA 在这种模式下所有的I/O 只在配置期间有效。在配置完成后,不用的I/O 将被浮空M2,M1,M0 三个选择开关对应于ML507 开发板上的SW3开关中的4,5,6位,在FPGA 上电之前将上述开关拨为0,0,1状态。

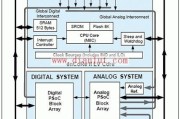

FPGA 工作原理

一个典型的FPGA 是有几个部分构成的,首先是逻辑块(LogicBlock),Altera 公司将其称之为逻辑阵列快(LAB)Xilinx 公司将其称为可配置逻辑块(CLB)。LAB 由称之为LE(Logic Element)的基本单元构成,CLB 由称之为LC(Logic Cell)的基本单元构成。这些就是FPGA 的逻辑资源,还有一部分是散落在各个逻辑块之间地内部连线,它们好比是PCB 板上的导线,将FPGA 内部地各个逻辑相连接,起点和终点都是IOB(I/O Block)。另一部分就是IOB 了,IOB 是FPGA的外部物理接口,类似IC 的各引脚,当然这里是根据用户需要自己可以任意定义的。如今的FPGA 的IOB 已经很强大, 从基本的LVTTL/LVCOMS 接口到PCI/LVDS/RSDS 甚至各种各样的差分接口,FPGA内部的I/O 实际上是分组的,但是每一组都可以灵活配置,改变上拉下拉电阻,调解驱动电流大小,兼容5V,3.3V,2.5V,1.8V 甚至1.5V,可以满足不同的电器特性,不同的I/O 接口物理特性以及外部硬件电路对输入输出信号的各种匹配要求。目前I/O 可以达到的频率也愈来愈高,通过特定的技术数据读取速率甚至可以达到2Gbps 现在越来越多的工程师喜欢FPGA,强大的I/O 特性也是一种原因吧。

图2-1 典型的FPGA内部结构图

TOP3 FPGA数字核脉冲分析器硬件电路

I/O 兼容恐怕是大势所趋。设计IOB 的概念和技术还有很多,这里不做介绍了。还有一部分就是FPGA 内部的功能模块,是制造商根据实际需要放置在FPGA 内部的。比如数字时钟管理模块即DCM,Xilinx 公司的FPGA 全都具有这种功能。比如相位环路锁定。PLL 需要一个外部时钟输入(晶振),经过内部处理后(包括分频和倍频)可以提供在频率和相位上都比较稳定的一定范围内的时钟。还有不得不提的内部不占用逻辑资源的块RAM。RAM 块可用作为单口RAM、双口RAM、内容地址存储器以及FIFO(first in first out)等常用存储器甚至ROM,移位寄存器。这对于小量数据缓存很有用,强化了FPGA的应用性。在选择FPGA 时,芯片内部块RAM 的资源多少也是衡量的一个重要因素。单独块RAM 的容量为18kbit 宽为18Bit、深度为1024,可以根据实际需要改变其位宽和深度,但有两点限制:首先就是修改后块RAM 的容量(位宽深度)不能大于单片块RAM 容量;而且位宽最大不能超过36Bit,可以将多片块RAM 联起来形成内存更大的RAM,此时只受限于芯片内块RAM 的数量,而不再受上面两条原则约束。不过在Quartus 中,具体操作起来很方便。还有底层内嵌功能单元包括内嵌专用硬核如乘法器等。它对于数字信号的运算处理提供极大的便利。

SPI 接口控制电路

图4-1 SPI模式连接图

该工程模块的SPI 接口四条信号线分别定spi_cs_n,spi_clk,spi_miso 和spi_mosi。其中spi_cs_n 是数据控制使能信号,当要对芯片进行操作时,此信号低电平有效。也就是说在同一条主线上可以连接多个SPI。spi_clk是SPI 同步时钟信号,数据信号在该时钟的控制下进行逐位传输。spi_miso 和spi_mosi 是主从机进行通信的数据信号,spi_miso即主机的输入或者说是从机的输出spi_mosi 即主机的输出或者说是从机的输入。

VGA 显示驱动模块

标准VGA 一共有15 针,真正用到的接口不多,只有5 个,场同步信号和列同步信号是为了让VGA 接收部分知道过来的数据是对应哪一行哪那一列。还有三原色信号,本课题硬件三原色信号通过连接不同的电阻后直接与I/O 接口相连(可理解为简易的DA 转换),这样就可以显示256 色了。内部VGA 与FPGA 接口如图7-1 所示。

图7-1 VGA 内部简化DA

FPGA 器件应用是继单片机之后,当今地嵌入式系统开发应用中最最热门的关键技术之一,并且随着制造工艺水平的不断提高,成本的不断下降,FPGA 甚至大有替代专用ASIC 的趋势。FPGA 使用Verilog 或VHDL 等硬件描述语言编程。系统工程所有功能全部使用FPGA 来完成,内容包括SD 卡的读取控制,图片解码,VGA 驱动显示等等,采用的是SF—EP1开发板,该板FPGA 使用EP1C3T144C8,配置PLL 电源电路,SD 接口,1 个256 色的VGA 通用接口,SDRAM 等。支持AS 及JTAG 配置方式,软件平台使用Quartus Ⅱ 9.1,从而完成10 幅800*600 的BMP 图片循环显示。

FPGA数字核脉冲分析器硬件电路

多道脉冲幅度分析仪和射线能谱仪是核监测与和技术应用中常用的仪器。20世纪90年代国外就已经推出了基于高速核脉冲波形采样和数字滤波成型技术的新型多道能谱仪,使数字化成为脉冲能谱仪发展的重要方向。国内谱仪技术多年来一直停留在模拟技术水平上,数字化能谱测量技术仍处于方法研究阶段。为了满足不断增长的高性能能谱仪需求,迫切需要研制一种数字化γ能谱仪。通过核脉冲分析仪显示在显示器上的核能谱帮助人们了解核物质的放射性的程度。

图1即为总体设计框图,探测器输出的核脉冲信号经前端电路简单调理后,经单端转差分,由采样率为65 MHz 的高速ADC 在FPGA 的控制下进行模/数转换,完成核脉冲的数字化,并通过数字核脉冲处理算法在FPGA 内形成核能谱,核能谱数据可通过16 位并行接口传输至其他谱数据处理终端, 也可通过LVDS/RS 485接口实现远程传输。特别需要注意的是,由于高速AD 前置,调理电路应该满足宽带、高速,且电路参数能够动态调整的需要,以适应不同类型探测器输出的信号,从而更好地发挥数字化技术的优势。

前端电路

前端电路由单端转差分和高速ADC 电路组成。差分电路由于其良好的抗共模干扰能力而应用广泛。由于调理电路输出的脉冲信号为单极性信号,若直接送入ADC,将损失一半的动态范围。设计中在运放中加入一个适当的偏置电压,将单极性信号转换成双极性信号后再送入ADC,以保证动态范围。将信号由单端转换成差分的同时,进行抗混叠滤波处理,完成带宽的调整。

本设计使用AD9649 - 65 高速ADC 实现核脉冲的模/数转换,AD9649为14 位并行输出的高速模/数转换器,具有功耗低、尺寸小、动态特性好等优点。当信号从探测器通过调理电路,过差分转单端电路后,以差分信号的形式进入ADC, 在差分时钟的控制下,转换成14 位数据,进入FPGA.该高速A/D 在外部FPGA 的控制下对信号进行采样。然后将采样后的数字信号送入FPGA 中实现数字核脉冲的幅度提取。图2 为A/D 转换的原理图,AD9649在差分时钟的同步下完成A/D 转换,D0~D13为14个有效输出数据位。

TOP4 揭秘FPGA电机测速系统经典电路

目前国内外多道脉冲幅度分析的数字化实现主要有2种方案:纯DSP 方案、DSP+可编程器件方案。本文将充分发挥FPGA 的并行处理优势,在单片FPGA芯片上实现核脉冲的采集与数字核脉冲处理算法,经Quar-tus-Ⅱ软件仿真与综合,本文选用EP3C40 FPGA 芯片实现多道分析器的数字化功能。

接口电路设计采用了LVDS 和RS485两种长距离数据传输接口,用于实现核能谱数据的远程传输。LVDS 即低电压差分信号,是一种可以实现点对点或一点对多点的连接,具有低功耗,低误码率,低串扰,低噪声和低辐射等特点。LVDS 在对信号完整性、地抖动及共模特性要求较高的系统中得到了越来越广泛的应用。图3为低电压、最高数据传输速率为655 Mb/s 的LVDS 接口电路。

揭秘FPGA电机测速系统经典电路

外围电路设计

传感器将电机转速的模拟信号转换成数字脉冲信号送入FPGA 模块。同时由基准时钟电路产生准确的时钟信号和复位电路产生的复位信号送入FPGA 模块。再由FPGA 模块产生分频电路、十进制计数器电路、数据处理电路和显示译码电路。由分频电路将送入的基准时钟信号进行分频,得到一个闸门信号,作为十进制计数器的使能信号。数据处理电路的作用是将十进制计数器得到的数据进行相应的处理后,再送入显示译码电路进行转换译码。电机测速系统的总体框图如图1所示。外围电路分为:基准时基电路,复位电路,传感器测量电路和显示电路。

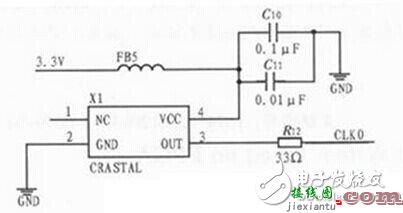

图2 有源晶振电路图

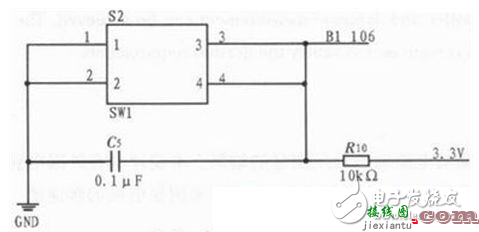

复位按键的设计

按键作为嵌入式智能控制系统中人机交互的常用接口,我们通常会通过按键向系统输入各种信息,调整各种参数或者发出控制指令,按键的处理是一个很重要的功能模块,它关系到整个系统的交互性能,同时也影响系统的稳定性。在本次设计中,通过按键实现了FPGA模块的手动复位。复位按键如图3所示。

图3 复位按键电路图

显示电路的设计

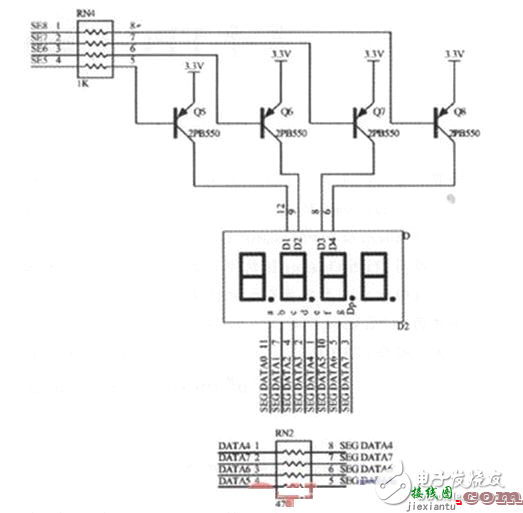

在本次设计中我们用到的显示电路如图4 所示。

由数码管显示电路可以知道,这是共阳极数码管。当在位选端SE1~SE4输入低电平时,三极管导通,从而D1~D4接入高电平。由a 到DP 端输入数码管显示码,就可以得到我们所需要的数字,由位选端让数码管选择导通。

本次设计是基于FPGA 的电机测速系统设计,利用的是Altera 公司开发的Quartus II 软件作为设计平台,可以在FPGA 开发板上实现测量由传感器转换得到的脉冲信号,并且通过计算得到电机转速值。在本次设计中,还可以进行一些扩展,可以添加报警电路,设定一个报警值,当测量的转速值大于这个报警值时,就可以让蜂鸣器报警或数码管点亮。

TOP5 FPGA数字变换器控制电路设计攻略。

系统结构和工作原理

系统设计时,采用模块化设计的思想,按照技术指标设计各个功能模块,通过各模块之间的协调配合完成系统的测试任务。系统的整体结构框图如图1所示,整个系统由计算机、USB 芯片FT245、两片FPGA、输出电源电压控制模块、计算机字信号发送模块、勤务信号发送模块、计算机字数码与指令数码接收模块和指令信号发送模块组成。模块化设计能够使在进行系统调试和硬件编程时,简单、快速的定位并解决问题。

硬件电路选用XILINX 公司的XC3S200-208和XC2S100-208两片FPGA 作为系统的逻辑控制中心,其中XC3S200-208作为主控芯片,主要实现对上位机的命令接收和判断,进而产生和发送计算机字信号,接收计算机字数码和指令数码并编帧、上传数据至上位机;XC2S100-208作为从控制芯片,完成128路指令信号的发送;两片FPGA 之间采用串行通信的方式发送控制命令来实现通讯。另外,通过上位机软件可以实现向系统发送复位或停止命令,这样能够减少硬件的功耗并提高测试系统的工作效率。

USB 接口模块实现

USB 具有成本低、通用性好、连接简单、支持热拔插等特点,而从系统实际的速率传输要求出发,设计采用通用USB 接口芯片FT245BM 实现与上位机的通信。FT245BM 主要的功能是在内部逻辑的作用下实现数据串/并双向转换,它的最大传输速率可以达到M/s.FT245BM 免去了复杂的固件编程及驱动程序的编写,能够简化USB 的接口设计,为系统节省设计时间。

FT245BM 的8位数据线D7~D0、读信号RD、写信号WR、发送使能TXE、接收数据完毕信号RXF 与FPGA 连接,来完成两者的通信。计算机通过应用程序、动态链接库的有效配合将控制命令信号发送到FT245BM,FPGA 利用与之相连的I/O 口接收下发的控制命令或是发送上传的测试数据。

输出电源电压控制模块实现

由于需要为被测数字量变换器提供3档工作电压25V、28V、31V,在电源模块输出端连接三种不同阻值的电阻,就可以实现3种电压的切换,实现控制的电路如图3所示。

图中VCON+,VCON-为电源模块的输入电压,R25、R26、R27三组电位器用来调节电阻。25VCON、31VCON 分别与FPGA 的I/O 相连,是FPGA 给出的控制信号,电路中三极管的作用是利用其电流放大来增加信号的驱动能力。通过FPGA 对控制命令的判断来实现3档电压的控制。此外,系统的默认及复位的输出电压为28V。

计算机字信号发送模块实现

由于要求计算机字和移位脉冲的幅值都为8~10V,所以电路中采用运算放大器电路对FPGA 输出的信号进行放大来获取所需幅值的信号。计算机字信号发送电路如图4所示。

为了满足输出信号的精度和电流驱动能力的要求,本模块中采用AD 公司的运放AD811来设计电路。此运算放大器是高速运放,采用双电源供电,2500V/us 是其最高转换速率,具有较低的电流、电亚噪声。设计中采用同相放大电压串联型负反馈电路,输出电压稳定并且反馈效果好。电路中R83的接地是为了尽量减小由于偏置电流引起的电压失调,其阻值等于R22和R60的并联阻值,为R22//R60=666Ω。

TOP6 勤务信号发送模块实现

计算机字信号和指令信号都有相应的勤务信号来满足时序要求,一般勤务信号就是指帧、码同步信号,对其他信号的产生和接收起到时序基准同步的作用。指令勤务信号的电路原理如图5所示。计算机字勤务信号与其原理相同。根据系统的信号输出要求,即帧、码同步信号的幅值和电流驱动能力的要求,采用非门芯片 SN5405J 作为驱动电路来满足设计要求。

数码接收模块实现测试系统需要接收经变换器处理之后的信号,变换器以数码方式回传给测试系统,包括计算机数码和指令数码,两者的接收原理相同。设计采用光耦隔离的方式对数码信号进行接收,其电路原理图如图6所示。

光电耦合器采用TI 公司的HCPL-2631,它具有电绝缘能力和抗干扰能力,并且能有效的抑制各种噪声和尖峰脉冲干扰。它的两个输入端分别接收计算机字数码和指令数码,其中在光耦输入端连接的二极管作用是用来防止信号反跳造成内部二极管烧坏。

指令信号发送模块实现

指令信号是指一种断开或闭合的开关量信号。此模块的128路指令信号全部采用光耦继电器来实现,依据参数要求选择AQY210作为控制开关的器件,它的特点是耐高压,反应速度快,使用时间长。其单路指令信号发送电路原理如图7所示。

由由于指令信号的路数比较多,如果FPGA 的I/O 口输出直接驱动AQY210,势必会增加FPGA 的功耗。因此采用三极管对FPGA 的输出信号进行电流放大来提高控制信号的驱动能力。本设计采用NPN 型三极管3DK103,图中3order1是FPGA 的输出信号,其为‘0’时,三极管截止;其为‘1’时,三极管处于电流放大,流经光继电器发光管的电流13mA 足以使AQY210导通。

设计方案

图1为系统设计总体框图。该系统采用C8051系列单片机中的 C8051F121作为控制器,CvcloneⅢ系列EP3C40F484C8型FPGA为数字信号算法处理单元。系统设计遵循抽样定理,在时域内截取一段适当长度信号,对其信号抽样量化,按照具体的步骤求取信号的频谱,并在LCD上显示信号的频谱,同时提供友好的人机会话功能。该系统最小分辨率为1 Hz,可分析带宽为0~5 MHz的各种信号。

TOP7 采用FPGA频谱分析仪系统电路

AGC电路

输入信号经高速A/D采样,信号幅度必须满足A/D的采样范围,最高为2-3V,因此该系统设计应加AGC电路。AGC电路采用AD603型线性增益放大器。图3为AGC电路。

A/D转换电路

ADS2806是一款12位A/D转换器,其特点为:无杂散信号动态范围(SFDR)为73 dB;信噪比(SNR)为66 dB;具有内部和外部参考时钟;采样速率为32 MS/s。图4为ADS2806的电路。为使A/D转换更稳定,在A/D转换器的电源引脚上增加滤波电容,抑制电源噪声。该电路结构简单,在时钟CLK的驱动下,数据端口实时输出数据,供FPGA读取。

FPGA及外围接口模块

选用CycloneⅢ系列 EP3C40F484型FPGA,该器件内部有39 600个LE资源,有1 134 000 bit的存储器,同时还有126个乘法器和4个PLL锁相环。由于该器件内部有大量资源,因而可满足其内部实现数字混频、数字滤波、以及FFT运算。FP -GA正常工作时,主要需要的外部接口有:时钟电路、JTAG下载电路、配置器件及下载电路。图5为FPGA的外围接口电路。

该系统能够方便地在LCD上显示信号的频谱结构图。操作简单,便于学生进行操作,有助于实验教学课上学生更直观认识信号频谱结构,从而促进实验课教学。

TOP8 FPGA开发配置模式电路设计精华集锦

FPGA共有四种配置模式:从串模式(Slave Serial),主串模式(Master Serial),从并模式(Slave Parallel/SelectMap)以及边界扫描模式(Boundary-Scan)。具体的配置模式由模式选择引脚M2﹑M1﹑M0决定。不同的配置模式所对应的M2﹑M1﹑M0,配置时钟的方向以及相应的数据位宽。

主串模式——最常用的FPGA配置模式。

在主串模式下,由 FPGA 的 CCLK 管脚给 PROM 提供工作时钟,相应的 PROM 在 CCLK 的上升沿将数据。从 D0 管脚送到 FPGA 的 DIN 管脚。无论 PROM 芯片类型 ( 即使其支持并行配置 ),都只利用其串行配置功能。

主串配置电路最关键的 3 点就是 JTAG 链的完整性、电源电压的设置以及 CCLK 信号的考虑。

多片FPGA通信:

SPI串行Flash配置模式:

串行 Flash 的特点是占用管脚比较少,作为系统的数据存贮非常合适,一般都是采用串行外设接口 (SPI 总线接口 )。

FPGA 通过 SCLK 控制双方通信的时序,在 SS_n 为低时,FPGA 通过 MOSI 信号线将数据传送到 FLASH,在同一个时钟周期中,FLASH 通过 SOMI 将数据传输到FPGA 芯片。无论主、从设备,数据都是在时钟电平跳转时输出,并在下一个相反的电平跳转沿,送入另外一个芯片。在串行模式下,需要微处理器或微控制器等外部主机通过同步串行接口将配置数据串行写入 FPGA 芯片,其模式选择信号 M[2:0]=3’b111。

TOP9 重串模式的多片FPGA通信

DIN 输入管脚的串行配置数据需要在外部时钟CCLK 信号前有足够的建立时间。其中单片FPGA 芯片构成了完整的JTAG 链,仅用来测试芯片状态,以及支持 JTAG 在线调试模式,与从串配置模式没有关系。外部主机通过下拉 PROG_B启动配置并检测 INIT_B 电平,当 INIT_B 为高时,表明 FPGA 做好准备,开始接收数据。此时,主机开始提供数据和时钟信号直到 FPGA 配置完毕且 DONE 管脚为高,或者 INIT_B 变低表明发生配置错误才停止。整个过程需要比配置文件大小更多的时钟周期,这是由于部分时钟用于时序建立,特别当 FPGA 被配置为等待 DCM锁存其时钟输入。

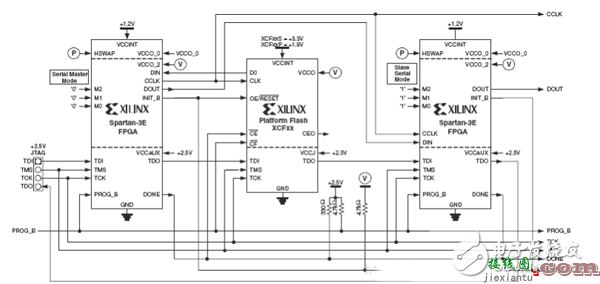

以下是重串模式的多片FPGA通信:

JTAG配置模式:

将模式配置管脚设置为 JTAG 模式,即 M[2:0]=3’b101时,FPGA 芯片上电后或者 PROG_B 管脚有低脉冲出现后,只能通过 JTAG 模式配置。JTAG 模式不需要额外的掉电非易失存储器,因此通过其配置的比特文件在 FPGA 断电后即丢失,每次上电后都需要重新配置。由于JTAG 模式已更改,配置效率高,是项目研发阶段必不可少的配置模式。

System ACE配置方案:

随着 FPGA 成为系统级解决方案的核心,大型、复杂设备常需要多片大规模的 FPGA。如果使用 PROM 进行配置,需要很大的 PCB 面积和高昂的成本,因此很多情况下都利用微处理由从模式配置 FPGA 芯片,但该配置方案容易出现总线竞争且延长了系统启动时间。为了解决大规模 FPGA 的配置问题,赛灵思公司推出了系统级的 System ACE(Advanced ConfiguraTIon Environment) 解决方案。

System ACE 可在一个系统内,甚至在多个板上,对赛灵思的所有 FPGA 进行配置,使用 Flash 存储卡或微硬盘保存配置数据,通过 System ACE 控制器把数据配置到 FPGA 中。目前,System ACE 有 System ACE CF(Compact Flash)、System ACE SC(Soft Controller) 以 及 System ACE MPM(Muti-Package Module) 三 种。

TOP10 FPGA芯片最小系统电路设计攻略

FPGA是英文Field Programmable Gate Array 的缩写,即现场可编程门阵列。FPGA利用它的现场可编程特性,将原来的电路板级产品集成为芯片级产品,缩小体积,缩短系统研制周期,方便系统升级,具有容量大、逻辑功能强,提高系统的稳定性的同时兼有高速、高可靠性。可以在数字系统设计中完全由用户通过软件进行配置和编程,从而完成某种特定的功能。要研究的是Altera 公司推出的一款FLEX10K 系列芯片,通过学习该芯片的工作原理和使用特性,设计一个基于FLEX10K 芯片的最小系统,通过对该最小系统的设计让大家能够更好的了解FPGA,并对其产生浓厚的兴趣,为更多想要了解学习FPGA 的人们做个很好的开头。

复位和晶振电路原理图设计

一个芯片,尤其是可编程芯片,通常在上电的瞬间需要一个短暂的时间进行内部参数的初始化,这个时候芯片无法立即进入工作状态。通常称上电初始化这些工作为复位,完成这个功能的电路称之为复位电路。本FPGA 芯片使用的是低电平复位,支持上电复位和手动复位,RESET 按下之后产生低电平。

图4-2 复位电路原理图设计

晶振是为电路提供频率基准的元器件,通常分成有源晶振和无源晶振两个大类,无源晶振需要芯片内部有振荡器,并且晶振的信号电压根据起振电路而定,允许不同的电压,但无源晶振通常信号质量和精度较差,需要精确匹配外围电路(电感、电容、电阻等),如需更换晶振时要同时更换外围的电路。有源晶振不需要芯片的内部振荡器,可以提供高精度的频率基准,信号质量也较无源晶振要好。本FPGA 芯片采用50MHZ 的有源贴片晶振作为芯片工作的时钟输入(图4-3)。

图4-3 晶振电路原理图设计

蜂鸣器电路原理图设计

电路很简单,需要说明的是开发板上使用的是高品质的蜂鸣器,需要脉冲控制其发声。电路图中的晶体管当作开关来使用,当I/O 提供的驱动能力不够的时候,晶体管能增强驱动能力。低电平有效(图4-4)。

图4-4 蜂鸣器电路原理图设计

开关电路原理图设计

最小系统板上使用的四腿按键实际上是分两组,每组中的两个是相通的,而两组直接是通过上面的按钮来控制通断状态的。简单理解成开关就可以了,按下去两端就形成短路,松开手就形成开路。短路相当于输入0,开路为1。另外需要说明的是,由于按键属于机械开关,按动过程不可避免存在抖动的现象,所以用户按下按键的时间可以稍微长一点(图4-5)。

图4-5 按键开关电路原理图设计

TOP11 八位拨码开关电路原理图

拨码开关就是相当与一个开关量,拨到ON 就表示接通,OFF 就是断开,在数字电路中对 0、1,通常用于二进制输入。本课题最小系统板使用八位拨码开关作为一个字节的输入,拨到ON 时相当于输入“1”,默认输入“0”(图4-6)。

图4-6 八位拨码开关电路原理图设计

JTAG 模式配置电路原理图设计

最小系统采用的FPGA 是Altera 公司的FLEX10K10 芯片,所以配置的PROM 选用的型号为EPC2LC20N,是20 脚的PLCC 封装,上拉电阻R4 是1K,其余的上拉电阻均是5K,TDI、TCK、TMS 和TDO 分别于JTAG 标准接口相连,完成配置电路的设计(图4-13)。

图4-13 JTAG 模式配置电路原理图设计

D 型并口下载线电路原理图设计

此下载线是由一个D 型25 针的并口与计算机相连接,10 针的一端与电路板相连接,数据的下载通过计算机直接配置,此下载线可以支持2.5V、3.3V 及5.0V 电压的下载模式,是一种可以通用型的下载线(图4-15)。

图4-15 D 型并口下载线电路原理图设计

最小系统电路设计的总体电路原理图

使用Altium 软件设计的电路原理图,FPGA 最小系统板包括时钟电路、复位电路、电源电路、JATG 电路、PROM 配置电路、显示模块电路、开关电路以及各种接口电路(图4-16)。

图4-16 最小系统电路设计的总体电路原理图

在当前国内外信息技术高速发展的今天,电子系统数字化已成为有目共睹的趋势。从传统的应用中小规模芯片构成电路系统到广泛地应用单片机,直至FPGA 在系统设计中的应用。电子设计技术已迈人了一个全新的阶段。FPGA 利用它的现场可编程特性,将原来的电路板级产品集成为芯片级产品,缩小体积,缩短系统研制周期,方便系统升级,具有容量大、逻辑功能强,提高系统的稳定性,而且兼有高速、高可靠性。越来越多的电子设计人员使用芯片进行电子系统的设计,通过基于FPGA 最小系统开发设计,说明了FAPG 芯片研究的动机和研究意义。

TOP12 基于FPGA水磁无刷直流电机控制电路

主要介绍基于现场可编程门阵列及EDA方法学的永磁无刷直流电机控制系统的电子电路设计。FPGA是一种高密度可编程逻辑器件,其逻辑功能的实现是通过把设计生成的数据文件配置进芯片内部的静态配置数据存储器来完成的,具有可重复编程性,可以灵活实现各种逻辑功能。

与ASIC不同的是,PCA本身只是标准的单元阵列,没有一般IC所具有的功能,但用户可以根据需要,通过专门的布局布线工具对其内部进行重新编程,在最短的时间内设计出自己专用的集成电路,从而大大提高了产品的竞争力。由于它以纯硬件的方式进行并行处理,而且不占用CPU资源,所以可以使系统达到很高的性能。这种新的设计方法可以把A/D接口、驱动器接口、通信接口集成在一块芯片上,同时在算法上完成位置、速度甚至电流算法,从而实现真正的片上可编程系统(SoPC)。这将成为下一代高性能伺服控制器集成化设计的一个趋势。

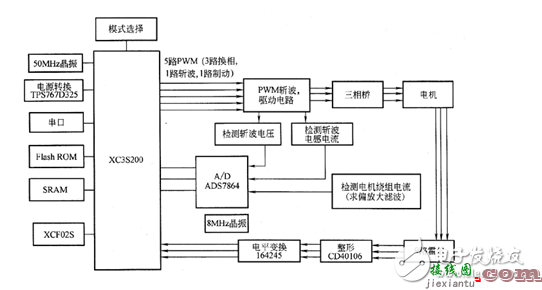

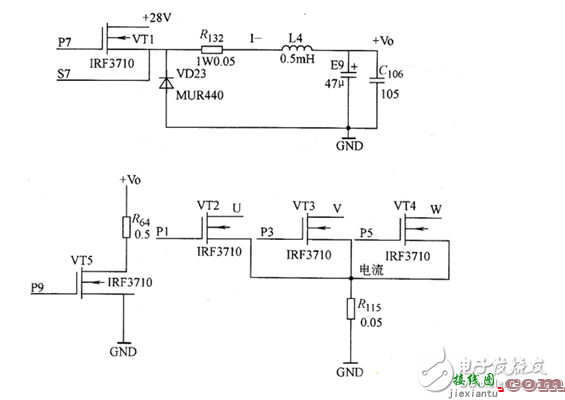

下面针对永磁无刷直流电机模块化设计的思想,介绍基于FPGA的控制系统的电子电路设计方法,其控制系统结构如图1所示。

图1 控制系统结构图

电路由电源模块,电压转化模块,FPCA模块,驱动电路模块,斩波电流、电压检测模块,绕组电流检测模块,A/D模块,通信模块,外扩存储器模块等部分组成。

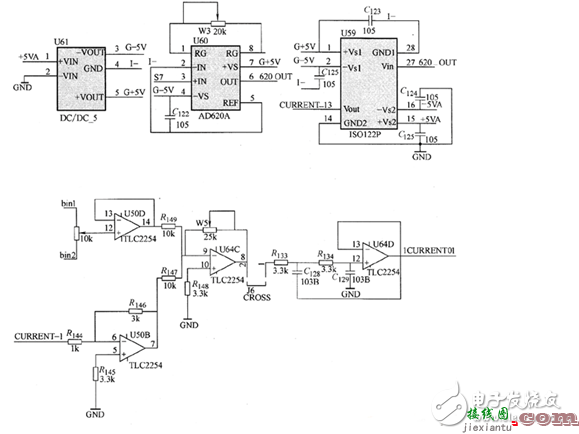

图2 斩波器电感电流检测电路

永磁无刷直流电机电枢电流检测信号调理电路和DC/DC BUCk变换器输出电压检测信号调理电路参见图3-16c和d,其功率电路如图3所示。

首先,由FPGA产生5路PWM波,其中3路用于永磁无刷直流电机换相,1路用于斩波,另1路用于再生能耗调节制动电流。三相换相PWM经驱动电路控制电机的换相,这3路PWM只用于换相不进行调制,由斩波环节进行调制。电机绕组电流经求偏、放大、滤波通过A/D(ADS7864)转换进人 FPGA(XC3S200),经PID调节器控制电流环;同样,斩波电压电流经滤波通过A/D转换也进人FPGA。图2所示为FPCA的最小系统电路,XCF02S为FPGA XC3S200的配置芯片,TPS767D325是电源芯片,将+5V电源电压转换为+2.5V和+3.3V供给FPGA,电源芯片LM317将+5V电源电压转换为+1.2V供给FPGA;FPGA的时钟选为50MHz,晶体振荡器为50MHz有源晶振,输出的时钟信号电压的高电平为+3.3V。

相关文章

发表评论