6 通道射频遥控器采用 CC2500 射频收发器模块和 microchip 的 PIC16F1847 微控制器设计。发射器配有 6 个轻触开关、4 个...

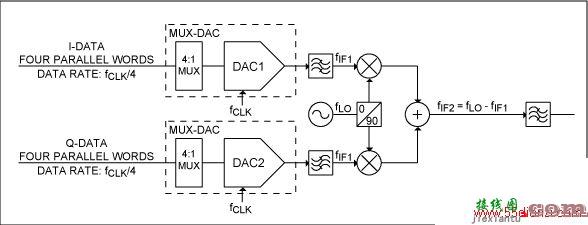

用DAC的I/Q发射器中的DAC和第一上变频级电路图

接线图

2023年02月02日 09:00 291

admin

使用具有多路输入的DAC(MUX-DAC)如MAX19692,或具有数据时钟输出的内插DAC时,输入数据速率为DAC刷新速率的1/N,DAC在一个或两个数据时钟跳变沿锁存数据。MAX19692中N=4,输入数据速率为DAC刷新速率的1/4。DAC输出一个由输入时钟经数字分频得到的数据时钟(DATACLK)。DAC上电时,数字时钟分频器可在N个状态的任意一个启动。如果使用多个DAC,不同DAC的时钟分频器会在不同的状态启动,所以DAC会在不同的时间锁存数据。除非这种情况被发现并校正,否则不同的DAC输出数据时相互之间可能会有一个或更多个时钟周期的延迟。如果每个DAC的时钟分频器可以复位,那么这种情况可以避免,但是仍然会存在一些问题。如果其中一个时钟分频器发生错误,DAC会变得永久异相,除非执行一些错误状态检测方法。为了保证系统的可靠性,必须检测相位错误状态并改正。如果DAC工作于非常高速的状态下,那么复位信号与输入时钟的同步也可能是个难题。

相关文章

发表评论