1 引 言 Multisim是加拿大Interactive Image Technologies公司近年推出的电子线路仿真软件EWB(Electron...

层次原理图设计

第4节 层次原理图的设计

加入收藏

加入收藏

转发分享

转发分享 人人网

人人网 开心网

开心网 新浪微博

新浪微博 搜狐博客

搜狐博客 百度收藏

百度收藏 谷歌收藏

谷歌收藏 qq书签

qq书签 豆瓣

豆瓣 淘江湖

淘江湖 Facebook

Facebook Twitter

Twitter Digg

Digg Yahoo!Bookmarks

更新于2008-07-07 13:53:24

Yahoo!Bookmarks

更新于2008-07-07 13:53:24

在进行电路设计时,一些简单的电路可以设计在一张图纸上。对于一些复杂的电路图,一张图纸往往不够用,解决这个问题的方法就是将复杂的电路分成多个电路,再分别绘制在不同的图纸上。这种方法称为层次原理图的设计。

一、主电路与子电路

层次原理图的设计思路是:首先把一个复杂的电路切分成几个功能模块,然后将这几个功能模块电路分别绘制在不同的图纸上,再以方块电路的形式将各功能模块电路的连接关系绘制在一张图纸上。这里的功能模块电路称为子电路,表示各功能模块电路连接关系的方块电路称为主电路。下面以Protel 99 SE自带的范例文件Z80 Microprocessor.ddb文件来说明主电路和子电路,该文件存放的位置是C:Program FilesDesign Explorer 99 SEExamples。

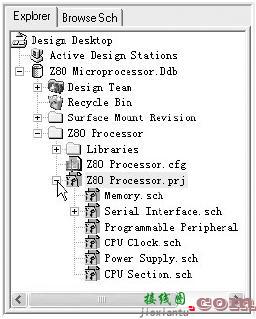

打开Z80 Microprocessor.ddb数据库文件后,在设计管理器的文件管理器中可以看到一个文件Z80 Processor.prj,如图2-126所示。该文件即为主电路文件,又称项目文件,其扩展名为.prj。单击该文件前的“+”号后展开该文件,可以看到它包含六个子电路文件,子电路文件的扩展名是.sch。

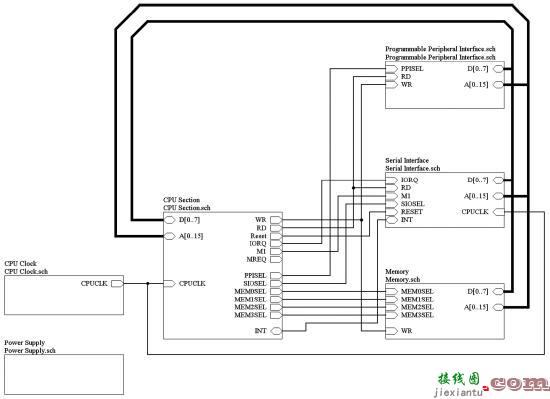

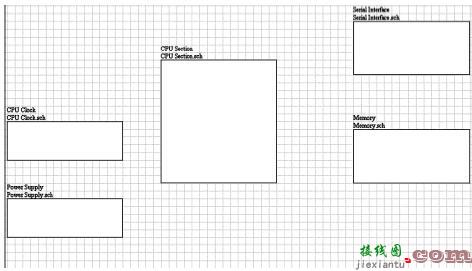

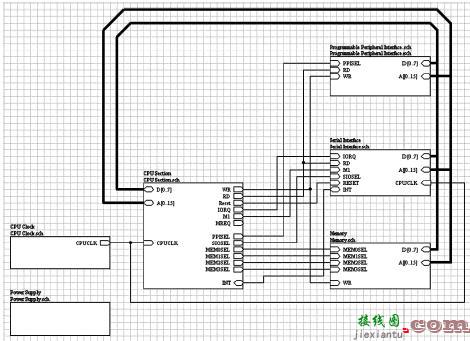

单击文件管理器中的主电路文件“Z80 Processor.prj”,可以在右边的工作窗口中看到该电路,如图2-127所示。从主电路可以看出,它由六个方块构成,每个方块表示一个子电路;主电路还通过端口和导线将子电路之间的连接关系表示出来。

图2-126 Z80 Microprocessor.ddb数据库文件结构

图2-126 Z80 Microprocessor.ddb数据库文件结构

图2-127 主电路Z80 Processor.prj

图2-127 主电路Z80 Processor.prj

在文件管理器中单击主电路文件Z80 Processor.prj下的子电路文件Memory.sch,可以看到该电路,如图2-128所示。从图中可以看出,子电路实际上就是电路原理图,它通过七个端口与其他子电路进行连接,在主电路的该子电路方块上也有这七个端口。

设计管理器中的子电路文件Serial Interface.sch前有“+”,表示它下面还有文件,展开后可以看到它的子电路Serial Baud Clock.sch。先打开Serial Interface.sch文件,如图2-129所示。从图中可以看出,该电路中除了元件外,还有一个方块,表示该电路下面还有子电路,此子电路就是Serial Baud Clock.sch,打开的Serial Baud Clock.sch子电路文件如图2-130所示。

图2-128 子电路Memory.sch

图2-128 子电路Memory.sch

图2-129 子电路Serial Interface.sch文件

图2-129 子电路Serial Interface.sch文件

图2-130 子电路Serial Baud Clock.sch

图2-130 子电路Serial Baud Clock.sch

综上所述,主电路以方块和端口的形式表示复杂电路的整体组成结构和各子电路的连接关系,子电路下面还可以有子电路,各个子电路由下到上连接起来即构成整个复杂电路。

二、由上向下设计层次原理图

由上向下的层次原理图设计思路是:先设计主电路,然后根据主电路图设计子电路。设计时要求主电路文件和子电路文件都放在一个文件夹中。

1.设计主电路

设计主电路的步骤如下。

第一步:建立项目文件夹。

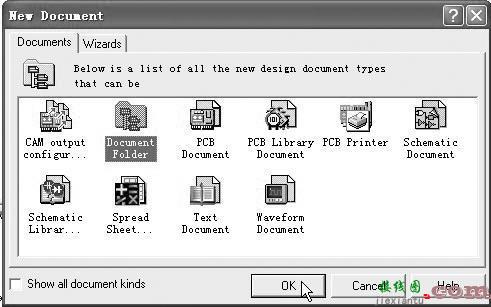

首先按照第1章介绍的方法建立一个数据库文件DZ3.ddb,然后在该数据库文件中建立一个项目文件夹。 建立项目文件夹的操作过程是:打开DZ3.ddb数据库文件,再执行菜单命令“File→New”,弹出New Document(新建文档)对话框,如图2-131所示,选择其中的“Document Folder(文件夹)”图标,再单击“OK”按钮,就建立了一个默认文件名为“Folder1”的文件夹,将该文件夹名改为“Z80”。

图2-131 新建文档对话框

图2-131 新建文档对话框

第二步:建立主电路文件。

建立主电路文件的操作过程如下:打开Z80文件夹,再执行菜单命令“File→New”,弹出新建文档对话框,选择其中的“Schematic Document”图标,再单击“OK”按钮,就建立了一个默认文件名为“Sheet1.sch”的文件,将该文件名改为“Z80.prj”。

第三步:绘制方块电路图。

绘制方块电路图的操作过程如下。

打开Z80.prj文件,再单击绘图工具栏中的![]() 按钮,或者执行菜单命令“Place→Sheet Symbol”,鼠标旁出现十字形光标,并且旁边跟随着一个方块。

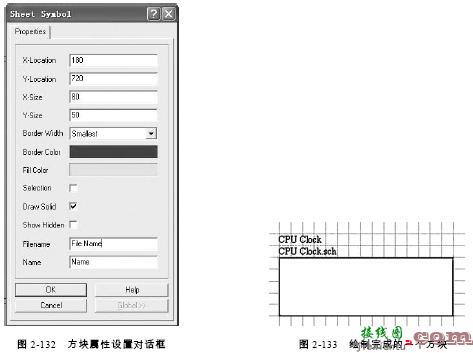

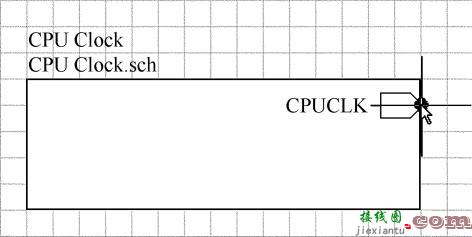

设置方块的属性。按键盘上的“Tab”键,弹出Sheet Symbol(方块属性设置)对话框,如图2-132所示,在对话框中将Fliename文本框设为“CPU Clock.sch”,将Name文本框设为“CPU Clock”,其他项保持默认值,再单击“OK”按钮。

将光标移到图纸上适当的位置,单击确定方块的左上角,然后将光标移到合适位置,单击确定方块的右下角,图纸上就绘制了一个方块,如图2-133所示,在方块旁出现刚才设置的文件名“CPU Clock.sch”和方块名“CPU Clock”。

再用同样的方法绘制其他方块,各方块绘制完成后的效果如图2-134所示。

按钮,或者执行菜单命令“Place→Sheet Symbol”,鼠标旁出现十字形光标,并且旁边跟随着一个方块。

设置方块的属性。按键盘上的“Tab”键,弹出Sheet Symbol(方块属性设置)对话框,如图2-132所示,在对话框中将Fliename文本框设为“CPU Clock.sch”,将Name文本框设为“CPU Clock”,其他项保持默认值,再单击“OK”按钮。

将光标移到图纸上适当的位置,单击确定方块的左上角,然后将光标移到合适位置,单击确定方块的右下角,图纸上就绘制了一个方块,如图2-133所示,在方块旁出现刚才设置的文件名“CPU Clock.sch”和方块名“CPU Clock”。

再用同样的方法绘制其他方块,各方块绘制完成后的效果如图2-134所示。

图2-134 绘制完成的各个方块

图2-134 绘制完成的各个方块

第四步:放置方块电路端口。

放置方块电路端口的操作过程如下。

单击绘图工具栏中的![]() 按钮,或者执行菜单命令“Place→Add Sheet Entry”,鼠标旁出现十字形光标。

将光标移到方块上单击,出现一个浮动的方块电路端口随光标移动,如图2-135所示。

设置方块电路端口的属性。按键盘上的“Tab”键,弹出Sheet Entry(方块电路端口属性设置)对话框,如图2-136所示。在对话框中,将Name项设为“CPUCLK”,I/O Type(输入/输出类型)项设为“Output”,Side(端口放置位置)项设为“Right”,Style(端口的样式)项设为“Right”,其他项保持默认值,再单击“OK”按钮即可。

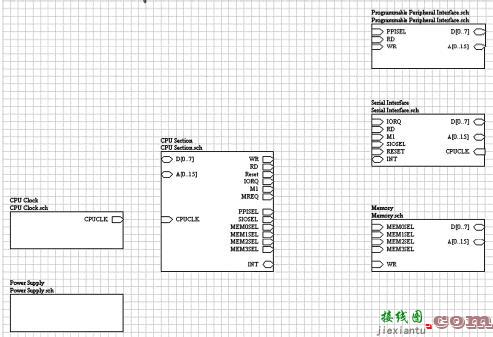

将光标移到方块上合适的位置,单击即在方块上放置好了一个端口,如图2-137所示。再用同样的方法放置其他端口,各个方块的端口放置完成后的效果如图2-138 所示。

按钮,或者执行菜单命令“Place→Add Sheet Entry”,鼠标旁出现十字形光标。

将光标移到方块上单击,出现一个浮动的方块电路端口随光标移动,如图2-135所示。

设置方块电路端口的属性。按键盘上的“Tab”键,弹出Sheet Entry(方块电路端口属性设置)对话框,如图2-136所示。在对话框中,将Name项设为“CPUCLK”,I/O Type(输入/输出类型)项设为“Output”,Side(端口放置位置)项设为“Right”,Style(端口的样式)项设为“Right”,其他项保持默认值,再单击“OK”按钮即可。

将光标移到方块上合适的位置,单击即在方块上放置好了一个端口,如图2-137所示。再用同样的方法放置其他端口,各个方块的端口放置完成后的效果如图2-138 所示。

图2-135 随光标移动的方块电路端口

图2-135 随光标移动的方块电路端口

图2-136 块电路端口属性设置对话框

图2-136 块电路端口属性设置对话框

第五步:连接方块电路。

将所有方块电路的端口放置好后,再用导线和总线将各方块电路的端口连接起来,如图2-139所示。将主电路中的各个端口连接好后,就完成了主电路的设计,设计完成的主电路如图2-140所示。

图2-137 放置完成一个端口

图2-137 放置完成一个端口

图2-138 放置完成所有端口

图2-138 放置完成所有端口

图2-139 用导线连接方块电路端口

图2-139 用导线连接方块电路端口

图2-140 设计完成的主电路

图2-140 设计完成的主电路

2.设计子电路

主电路设计完成后,利用主电路中的方块可以自动生成相应的子电路文件,而不需要重新建立。子电路的具体设计过程如下。

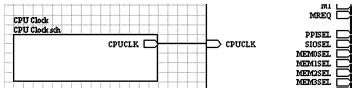

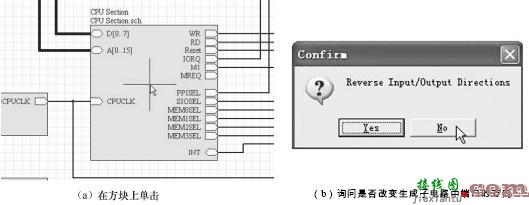

在主电路中执行菜单命令“Design→Create Sheet From Symbol”,鼠标旁出现十字形光标。 将光标移到需要生成子电路的方块“CPU Section”上单击,如图2-141(a)所示,弹出图2-141(b)所示的对话框,询问是否改变生成子电路中端口的方向,如果选择“Yes”,生成的子电路中的端口方向与主电路方块中的端口方向相反,即若主电路的方块中端口为输出,子电路相应的端口将变为输入,如果选择“No”,两者方向相同,这里单击“No”按钮。 选择对话框中的“No”后,文件管理器的主电路文件下自动生成CPU Section.sch子电路文件,同时在右边的工作窗口中可以看到图纸上有主电路的CPU Section方块上的所有端口,如图2-142所示。 用绘制电路原理图的方法,在子电路端口的基础上绘制出具体的子电路。 重复上述过程,设计出其他子电路,这样就完成了复杂电路的层次原理图设计。

图2-141 由主电路生成子电路操作

图2-141 由主电路生成子电路操作

图2-142 自动生成的子电路文件

图2-142 自动生成的子电路文件

三、由下向上设计层次原理图

由下向上的层次原理图设计思路是:先设计好各个子电路,然后根据子电路图生成主电路。设计时同样要求主电路文件和子电路文件都放在一个文件夹中。

1.设计子电路

设计子电路的过程如下。

① 建立子电路文件。首先建立一个数据库文件DZ4.ddb,然后在该数据库文件中建立一个项目文件夹Z80,再在Z80文件夹中建立一个默认文件名为“Sheet1.sch”的文件,将该文件名改为“CPU Clock.sch”。 ② 用设计电路原理图的方法绘制出CPU Clock.sch文件的电路原理图。 再用同样的方法设计出其他子电路的电路原理图。

2.设计主电路

设计主电路的过程如下。

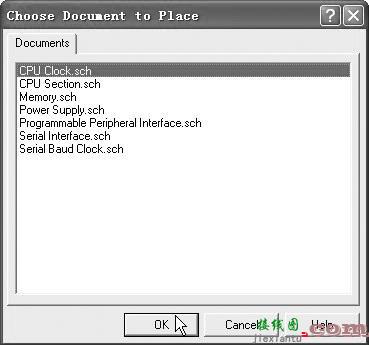

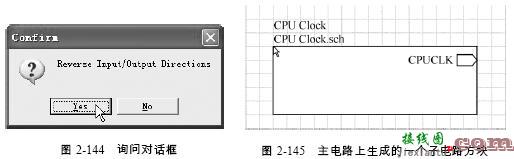

建立主电路文件。在数据库文件DZ4.ddb的Z80文件夹中建立一个文件名为“Z80.prj”的文件。 打开Z80.prj文件,再执行菜单命令“Design→Create Symbol From Sheet”,出现如图2-143所示的对话框。从中选择需要在主电路中转换成方块的电路,再单击“OK”按钮,又弹出一个对话框,如图2-144所示,询问是否改变生成主电路中方块端口的方向,这里选择“Yes”,鼠标旁出现十字形光标,并且旁边跟随着一个方块。 在图纸上合适的位置单击,方块便被放置在图纸上,并带有端口,如图2-145所示。 用同样的方法在主电路上放置其他子电路的方块图,将所有方块放置完后,再用导线和总线将各方块连接好。这样,一个由下向上的层次原理图就设计完了。

图2-143 选择生成方块的电子电路

图2-143 选择生成方块的电子电路

标签: 原理图设计

相关文章

发表评论