如图所示为数码相机/DV机电源供电电路,该电路以MAX1800芯片为控制核心。由图可知,数码相机都是采用电池供电.电压较低(0.7~5.5 V .但数...

大功率CPU核心电压供电电路的设计

1 引言

当今的高速中央处理器(CPU)在提供极高的性能的同时,对于其供电电源的各项指标的要求也达到了前所未有的高度。更高速的CPU需要更低的核心电压,却需要更大的功率,因此供电电路必须提供极大的电流。更好的解决核心电压的供电问题已经成为电压变换模块和PC主板设计者面临的极大挑战。

2 Intel相关规范对CPU核心电压的要求

Intel早期的CPU,如Pentium 2、Pentium 3都遵循Intel的VRM(Voltage Regulation Module)8.1~8.4电源规范,其最大输出电流值为22.6A。Tualatin核心的Pcntium 3及Celeron CPU则开始引入VRM8.5标准,其最大输出电流值为28AIntel在推出Willamette、NorthWood核心的Pentium4时引入了VRM9.O标准,其规定的最大输出电流为70A。随着Prescott核心Pentium 4的推出,VRM规范也更新到了VRD(Voltage Regulator Down)10.O,电流最大值也达到了91A。为了配合更高频率更高性能的CPU,200 5年4月Intel推出了VRDl0.1规范,对LGA775 Socket的CPU的供电电源的规格指标进行了细致的规定,这是对台式机CPU供电电源要求极高的电源规范,其要求列举如下:

(1)连续负载电流(ICCTDC)为115A;

(2)最大输出电流(ICCMAX)为125A;

(3)输出的电压值由VID[5:0]指定,范围为O.837 5~1.6V.以0.0125V为步进;

(4)负载线斜率(loadline slope)阻抗R0为1.00mΩ;

(5)最大电压纹波VRIPPLE为±5mV;

(6)最大电压上冲波峰VOS_MAX为50mv,其最长持续时间为25μs。

这里只是列举了最为重要的几个规定,VRDl0.1规范还有其他的许多内容,限于篇幅,这罩不再一一列举。由上述内容可见,高性能CPU对于供电电源电路的输出功耗需求越来越大,在VRDl0.1中要求输出功耗甚至高达170W以上。同时对于电压的精确性和稳定性的要求也达到了非常苛刻的地步,在大功率、大电流的情况下还要保持非常稳定和精准的负载线斜率。在VRDl0.O之前,CPU核心电压供电电路一般都是由三相或两相的PWM控制方式,这种方式已经无法满足100A以上的大电流需求。本文的设计使用了4相PWM控制,可以满足VRDl0.1的严格要求,以下详细叙述之。

3 大功率CPU核心电压电路的设计

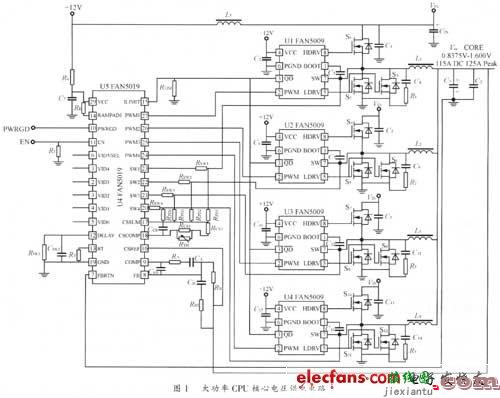

图l所示即为本文提出的满足VRD101要求的大功率CPU核心电压供电电路。它使用了仙童(Fairchild)公司的FAN50192—4相PWM电源控制器做为丰控制芯片。FAN5019控制4个Fairchild的FAN5009 MOSFET驱动器。FAN5009驱动开关外接的高端和低端M0SFET,然后通过电感与电容器件的充、放电对VCCCORE进行供电。

FAN5019是一款多相(最高支持4相)DC/DC控制器,专为产生高电流、低电压的CPU核心电压而设计。本设计中,它以并行的方式同时驱动四个PWM通道,而且以交叉开关的方式来减少输入、输出的纹波电流,这样可以达到减少外围器件,降低成本的目的。FAN5019采用了温度补偿电感器电流检测技术,来满足VRDl0.1规则的负载线技术要求,而一般的PWM控制器都是采用RDS(ON)或感应电阻器来测量电流和设置负载线,精度无法满足要求。如图1所示,FAN5019的VID[5:0]输入与VRDl0.l规范定义完全一致,可以控制输出0.8375~1.600V以12.5mV步进的电压,另外它还具有短路保护,电流上限可调,过压保护等增加安全可靠性的技术。FAN5019向每个FAN5009送出PWM控制信号,而FAN5009通过内部电路将其转换为可以正确驱动高端和低端M0SFET的信号输出。FAN5009可以同时驱动高端和低端的MOSFET,其内置启动二极管,因此无需在外围电路中再添加二极管。

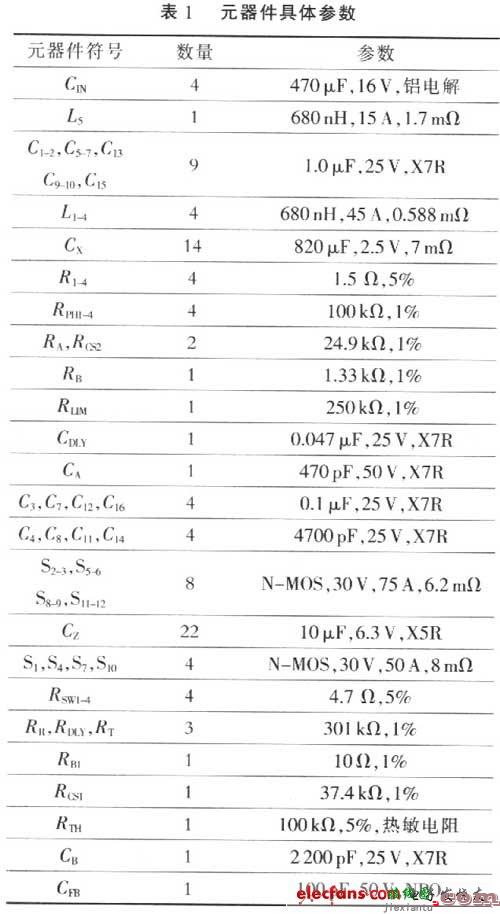

本设计的输入电压VIN为12V,额定输出电压VVID为1.500V,占空比D(Duty Cycle)为O.125,负载线斜率阻抗R0为1.OmΩ,ICCTDC大于115A,ICCMAX为125A,最大输出功耗为172.5W,最大电压纹波VRRIPLE为±5mV,每相的开关频率fSW设定为228kHz。外围元器什的具体参数如表l所列。

4 重要器件的选择与布局布线规则

4.1 功率MOSFET的选择

在选择高端和低端功率MOSFET时,主要考虑如下几个方面:

(1)较低的RDS(ON),应小于1OmΩ;

(2)尽可能高的导通电流;

(3)额定VDDS应该大于15V。

在选择低端MOSFET时,RDS(ON)是最重要的考虑因素,因为在正常工作时,低端的MOSFET导通时间较长,因而功率消耗较大。因此在本设计中.每相在低端都使用了两个FDD6682,其导通电流为75A,在VGS为10V时(正常工作状态),RDS(ON),为6.2mΩ,额定VDDS为30V。对高端的MOSFET而言,门电荷Qg也是重要的考虑因素,要求其越低越好,否则会影响开关速度进而影响功耗。因此在每相高端都使用了一个FDD6696,其导通电流为50A,在VGS为lOV时,RDS(ON)为8.0mΩ,额定VDDS为30V,门电荷为17nC,可以完令满足没计的要求。

4.2 输出电感的选择

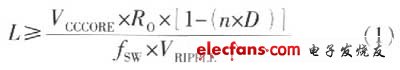

输出电感有3个主要指标,电感量L、额定电流值Irated和直流电阻RDCR,电感的额定电流值是电感线圈的饱和电流或过热电流中较小的值。为使4相的输出电流总量大于等于125A,每相的输出电感额定电流应大于等于31.25A。电感量的取值与工作频率,纹波电流等因素都有一定的相关,可以根据式(1)进行计算:

式中:VCCCORE为输出电压;RO负载线斜率电阻;n为相数;D为每一相的占空比;fSW开关频率;VRIPPLE为最大纹波电压。

根据前面提到的设计参数,可以计算得输出电感的电感量应该大于658nH。电感的直流电阻RDCR最好取值在R0的O.5倍到l倍之间,这是因为,电感的RDCR会用来监测每相的输出电流,如果RDCR值太小,会引起较大的测量误差,影响设计的正常运行,如果RDCR值太大,又会造成较大的能量损耗,影响设计的效率。因此,我们选用了线艺电子(Coilcraft)公司的电感SER2009—681ML,其额定电流为45A,电感量为680 nH,直流电阻为0.588mΩ,完全满足设计对输出电感的要求。

4.3 布局布线

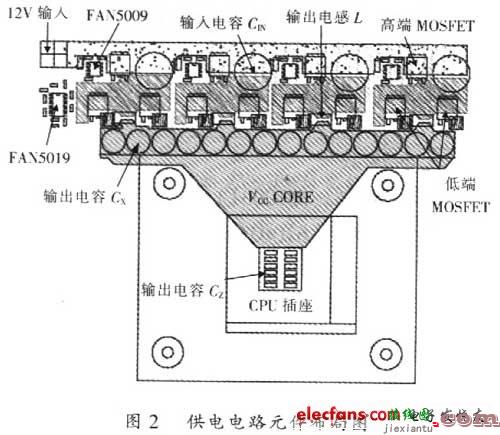

布局布线对电路稳定性、精确性的最终实现起着至关重要的作用,图2是本设计在4层PCB上的布局图,遵循如下的布局布线规则。

(1)输入电容CIN必须放置在尽量靠近高端MOSFET的漏极,其阴极应该放置在靠近低端MOSFET的源极,且每柑都应该至少放置一个输入电容。

(2)每相的FAN5009驱动器应该靠近各相的MOSFET。

(3)FAN5019应该放置在靠近COUT但是远离CIN的阴极和低端MOSFFT的源极处。其周围的元件应该放置在尽量靠近它的位置,并且它们与FAN5019之间应该用尽量粗的线来连接。FB和CSSUM两个引脚的线是最为重要的,应尽量短,且远离其他线。FAN5019及其周围的元件应该使用独立的模拟地平面(包括其底下的PCB电源层平面)来接地。

(4)因为设计的电流非常大,因此在PCB各层之间传输电流时要尽可能多州穿孔以减小电流通路的电阻和电感效应,粗略的估算方法是1mm直径的穿孔可以允许3A电流。穿孔还可以帮助IC散热。

(5)输出电容CX及CZ应该尽町能靠近CPU的插座或CPU引脚。

(6)供电电路相关的PCR走线都应该尽可能的宽,并且保持各自间距,以避免EMI问题。

(7)布局应合理紧凑,并且充分考虑散热问题。

5 实验结果

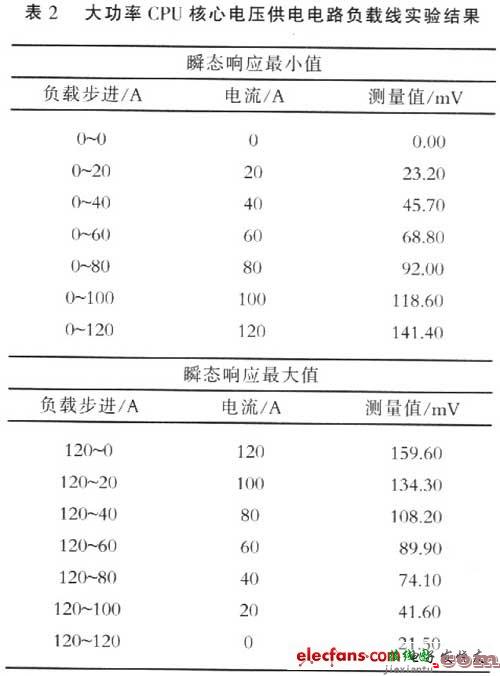

本文介绍的大功率CPU供电电路经过PCB样板制作和调试,已经达到正常工作的要求,表2为实验测量样板的输出电压负载线的结果。实验使用了Intel公司的Voltage Transient Test Tool进行电压瞬态响应的测试,测试节点为LGA775CPU插座的U27与V27引脚,VCCOORE=1.500V。从实验结果可见此电路的设计可以达到VRDlO.1要求。

6 结语

应用FAN5019设计的大功率CPU核心电压供电电路,不仅可以用于高性能台式机CPU,也可以用于工作站、服务器的CPU供电,因此具有相当的实用价值。

相关文章

发表评论