双联开关接线图双联开关接线图双联开关接线图【实战问题】 家用卫生间有个开关,是2个按纽的,一个控制镜前灯,另一个控制吸顶灯,开关呢,是松日的,有 6个...

用于比较器迟滞的 SPICE 测试台

接线图

2024年01月26日 10:49 197

admin

用于比较器迟滞的 SPICE 测试台

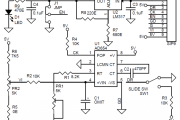

在本文的这一部分中,我们将使用图 1 中的测试设置来运行一些模拟。 用于测试目的的开环比较器电路的 LTspice 原理图。

我使用“diffschmtbuf”组件作为我的比较器。我在 SpiceLine 字段中为其指定的参数如图 2 所示。 SpiceLine 字段的屏幕截图,显示 diffschmtbuf 组件的参数。

让我们简要地看一下每个定义:

vhigh = 5:当同相输入 ( V + ) 的电压高于反相输入 ( V - ) 时,输出将为 5 V。

vlow = 0:当V + 的电压低于V -时,输出将为 0 V。

vt = 0:阈值电压为 0 V,这意味着当两个输入电压之差为 0 V时,输出将发生转变。

vh = 0:比较器具有 0 V 迟滞。使这个值非零肯定是比我们要做的更简单的添加磁滞的方法,但这样我们就不会学到任何有关磁滞电路的知识! 查看图 1 时,您可能已经注意到比较器符号内有一个熟悉的形状,我在图 3 中放大了该形状。

图 3.带迟滞的比较器的示意图。

这是典型磁滞曲线的简化版本。迟滞在比较器应用中起着如此重要的作用,以至于迟滞曲线有时会作为比较器示意图的一部分。 输入信号是通过串联连接两个电压源而产生的。第一个VR RAMP生成一个在 10 ms 内从 0 V 线性增加到 5 V 的信号。第二个V NOISE是振幅为 50 mV、频率为 10 kHz 的正弦曲线。图 4 显示了复合信号。

图 1 中比较器的电压图,无迟滞。

图 6.图 1 中电路的电压行为(无迟滞)。

从低到高的过渡看起来有点厚。果然,如果我们放大(图 7),我们会看到正弦噪声导致了多次转换。

图 1 中比较器的电压图没有迟滞,放大后可以清楚地显示由噪声引起的不需要的转换。

图 7.图 6 中的图的特写视图。注意由噪声引起的多个转换。

现在我们已经使用测试台来验证我们的设计,是时候介绍我们将在本文其余部分讨论的电路了。

迟滞反馈网络

滞后是我们需要正反馈而不是负反馈的罕见情况之一。图 8 显示了带有迟滞的基本比较器电路;请注意,其正反馈配置不会修改参考电平。相反,我们使用当前输出电压和当前输入电压来创建新信号。该信号是我们实际施加到比较器的非反相输入端子 ( V + ) 的信号。

LTspice 比较器,包括引起迟滞的分压器。

图 8.具有基于正反馈的迟滞的比较器的 LTspice 原理图。

从本系列的第一篇文章中我们知道,滞后的基本原理是利用系统的历史记录(或者更具体地说,输入和输出之间的相对运动)来影响系统对输入条件的响应。那么,我们从输出反馈信息是有意义的,因为输出的当前状态指示了有关先前输入活动的某些信息。

如果输出当前处于正轨,则意味着输入之前高于参考电平。为了使输入跨越参考电平,它必须减小。相反,如果输出当前处于负轨,则输入之前必须低于参考电平,并且如果超过参考电平则必须增加。 图 9 显示了当输入从 0V 开始增加且输出从负电源轨开始时会发生什么情况。非反相电压信号中的垂直跳变标识了输出转换的时刻。

图 9. 具有迟滞的比较器的V IN 、 V +和V REF 。输出从负轨开始。

当输出为 0 V 时,R1和R2形成分压器,其输出施加到非反相输入端子 (V + )。由于这种分压器效应,V +低于V IN并且以较慢的速率增加。结果是V +和V IN值之间的差异不断扩大。

V +相对于输入信号的下降意味着V +需要更长的时间才能达到参考电平 ( V REF )。从这个意义上说,尽管V REF实际上保持不变,但比较器的作用就好像参考电平现在更高了。 当V +达到参考电平 ( V REF ) 时,输出发生转变。请注意,这种情况发生在 V IN达到参考电平之后 - 滞后越大意味着对噪声的抵抗力越强,但它也会导致更多的转换延迟。 在图 10 中,输入斜坡在 10 ms 处反转方向。信号现在正在减弱,输出从正轨开始。如上例所示,电路的输出从负轨开始并增加,这会产生延迟。然而,电压效应是相反的:V +现在高于V IN 直到输出切换。 具有正反馈的模拟比较器的输入电压、参考电压和同相端电压。 输入信号最初增加,但随后达到峰值并开始减少。

创建单独的阈值

正轨输出电压产生低于V IN的V +,而负轨输出电压产生高于V IN的V +。然而,在这两种情况下,输入信号必须超过参考电平才能引起输出转换。 所有这一切的结果是一个系统,其中增加的输入信号具有一个阈值水平,而减少的输入信号具有另一个阈值水平。增加的信号必须高于高阈值电压 ( V TH );下降信号必须低于低阈值电压 ( V TL )。V TH和V TL之间的差值等于滞后量,在图 11 中标记为V HYST。V TH和V TL之间的空间称为滞后区。

图 11.滞后区。

输出转换后,信号波动必须达到另一个阈值才能引发新的转换。这样,滞后区就具有抗噪声能力。

想象一下噪声输入信号正在增加。最终它将跨越V TH,输出将转换到正轨。此后不久,噪声导致信号降至V TH以下。对此没有任何反应,因为信号现在正在减小,并且必须一直下降到V TL才能引起转换。

通过磁滞实现的抗噪声能力在图 12、13 和 14 中显而易见。水平虚线代表V TL和V TH。 具有迟滞和噪声信号的比较器的模拟操作。

图 13. V TH (高阈值电压)下的开关放大图。

在图 14 中,输出在低阈值电压 ( V TL )下切换。

图 12 中的放大图显示了低阈值电压下的输出电压切换。

图 14. V TL (低阈值电压)下开关的放大视图。

在本文的这一部分中,我们将使用图 1 中的测试设置来运行一些模拟。 用于测试目的的开环比较器电路的 LTspice 原理图。

我使用“diffschmtbuf”组件作为我的比较器。我在 SpiceLine 字段中为其指定的参数如图 2 所示。 SpiceLine 字段的屏幕截图,显示 diffschmtbuf 组件的参数。

让我们简要地看一下每个定义:

vhigh = 5:当同相输入 ( V + ) 的电压高于反相输入 ( V - ) 时,输出将为 5 V。

vlow = 0:当V + 的电压低于V -时,输出将为 0 V。

vt = 0:阈值电压为 0 V,这意味着当两个输入电压之差为 0 V时,输出将发生转变。

vh = 0:比较器具有 0 V 迟滞。使这个值非零肯定是比我们要做的更简单的添加磁滞的方法,但这样我们就不会学到任何有关磁滞电路的知识! 查看图 1 时,您可能已经注意到比较器符号内有一个熟悉的形状,我在图 3 中放大了该形状。

图 3.带迟滞的比较器的示意图。

这是典型磁滞曲线的简化版本。迟滞在比较器应用中起着如此重要的作用,以至于迟滞曲线有时会作为比较器示意图的一部分。 输入信号是通过串联连接两个电压源而产生的。第一个VR RAMP生成一个在 10 ms 内从 0 V 线性增加到 5 V 的信号。第二个V NOISE是振幅为 50 mV、频率为 10 kHz 的正弦曲线。图 4 显示了复合信号。

图 5 提供了放大视图。

图 1 中比较器的电压图,无迟滞。

图 6.图 1 中电路的电压行为(无迟滞)。

从低到高的过渡看起来有点厚。果然,如果我们放大(图 7),我们会看到正弦噪声导致了多次转换。

图 1 中比较器的电压图没有迟滞,放大后可以清楚地显示由噪声引起的不需要的转换。

图 7.图 6 中的图的特写视图。注意由噪声引起的多个转换。

现在我们已经使用测试台来验证我们的设计,是时候介绍我们将在本文其余部分讨论的电路了。

迟滞反馈网络

滞后是我们需要正反馈而不是负反馈的罕见情况之一。图 8 显示了带有迟滞的基本比较器电路;请注意,其正反馈配置不会修改参考电平。相反,我们使用当前输出电压和当前输入电压来创建新信号。该信号是我们实际施加到比较器的非反相输入端子 ( V + ) 的信号。

LTspice 比较器,包括引起迟滞的分压器。

图 8.具有基于正反馈的迟滞的比较器的 LTspice 原理图。

从本系列的第一篇文章中我们知道,滞后的基本原理是利用系统的历史记录(或者更具体地说,输入和输出之间的相对运动)来影响系统对输入条件的响应。那么,我们从输出反馈信息是有意义的,因为输出的当前状态指示了有关先前输入活动的某些信息。

如果输出当前处于正轨,则意味着输入之前高于参考电平。为了使输入跨越参考电平,它必须减小。相反,如果输出当前处于负轨,则输入之前必须低于参考电平,并且如果超过参考电平则必须增加。 图 9 显示了当输入从 0V 开始增加且输出从负电源轨开始时会发生什么情况。非反相电压信号中的垂直跳变标识了输出转换的时刻。

图 9. 具有迟滞的比较器的V IN 、 V +和V REF 。输出从负轨开始。

当输出为 0 V 时,R1和R2形成分压器,其输出施加到非反相输入端子 (V + )。由于这种分压器效应,V +低于V IN并且以较慢的速率增加。结果是V +和V IN值之间的差异不断扩大。

V +相对于输入信号的下降意味着V +需要更长的时间才能达到参考电平 ( V REF )。从这个意义上说,尽管V REF实际上保持不变,但比较器的作用就好像参考电平现在更高了。 当V +达到参考电平 ( V REF ) 时,输出发生转变。请注意,这种情况发生在 V IN达到参考电平之后 - 滞后越大意味着对噪声的抵抗力越强,但它也会导致更多的转换延迟。 在图 10 中,输入斜坡在 10 ms 处反转方向。信号现在正在减弱,输出从正轨开始。如上例所示,电路的输出从负轨开始并增加,这会产生延迟。然而,电压效应是相反的:V +现在高于V IN 直到输出切换。 具有正反馈的模拟比较器的输入电压、参考电压和同相端电压。 输入信号最初增加,但随后达到峰值并开始减少。

创建单独的阈值

正轨输出电压产生低于V IN的V +,而负轨输出电压产生高于V IN的V +。然而,在这两种情况下,输入信号必须超过参考电平才能引起输出转换。 所有这一切的结果是一个系统,其中增加的输入信号具有一个阈值水平,而减少的输入信号具有另一个阈值水平。增加的信号必须高于高阈值电压 ( V TH );下降信号必须低于低阈值电压 ( V TL )。V TH和V TL之间的差值等于滞后量,在图 11 中标记为V HYST。V TH和V TL之间的空间称为滞后区。

图 11.滞后区。

输出转换后,信号波动必须达到另一个阈值才能引发新的转换。这样,滞后区就具有抗噪声能力。

想象一下噪声输入信号正在增加。最终它将跨越V TH,输出将转换到正轨。此后不久,噪声导致信号降至V TH以下。对此没有任何反应,因为信号现在正在减小,并且必须一直下降到V TL才能引起转换。

通过磁滞实现的抗噪声能力在图 12、13 和 14 中显而易见。水平虚线代表V TL和V TH。 具有迟滞和噪声信号的比较器的模拟操作。

图 13. V TH (高阈值电压)下的开关放大图。

在图 14 中,输出在低阈值电压 ( V TL )下切换。

图 12 中的放大图显示了低阈值电压下的输出电压切换。

图 14. V TL (低阈值电压)下开关的放大视图。

相关文章

发表评论