双联开关接线图双联开关接线图双联开关接线图【实战问题】 家用卫生间有个开关,是2个按纽的,一个控制镜前灯,另一个控制吸顶灯,开关呢,是松日的,有 6个...

SiC器件短路事件失效模型分析

接线图

2024年01月28日 08:54 220

admin

由于人们对降低能耗和在高开关频率应用下运行的兴趣日益浓厚,碳化硅功率器件已成为一项有前景的技术。SiC 还可以承受高工作温度,使其成为工业环境的合适选择。宽带隙半导体器件的出现使工程师能够设计电力电子系统以满足特定的应用要求。1与 SiC 一样,氮化镓也属于宽带隙类别。设计任何电源系统之前需要考虑的一些主要因素包括成本、效率、功率密度、复杂性和可靠性。2

由于开关速度快和通态电阻低,SiC MOSFET 通常很容易因短路事件而损坏。3安徽工业大学电气与信息工程学院的研究团队提出了两种常用功率器件中 SiC 器件在短路事件中的失效模型:SiC MOSFET(Cree 的 N 沟道增强型 SiC MOSFET) )和 SiC JFET(通常采用英飞凌的 SiC JFET)。4

开发 SiC 晶体管在短路事件中的故障模型

Wang等人提出的论文中研究表明,在短路事件下,故障电流高于功率器件的额定电流。5这意味着漏电流会导致故障电流,为了验证这一点,使用了计算机辅助设计(TCAD)模拟技术。SiC JFET 和 SiC MOSFET 的电流分量描述了两个 SiC 晶体管中的空穴电流密度。分析执行的文件,我们可以得出结论,高密度空穴电流流过晶体管的N漂移区和P基极区之间的pn结。“TCAD仿真还表明,对于SiC MOSFET,高浓度载流子聚集在JFET区域的顶部;其中一小部分注入到栅极氧化物中,在高温和高电场强度的应力下形成栅极漏电流,”该团队解释道。

故障 - 短路事件前 SiC JFET(上)和 SiC MOSFET(下)中空穴电流密度的分布

SiC JFET和 SiC MOSFET失效模型原理图的设计考虑了漏电流的引入。虚线框中的结构是传统电路模型的一部分,与沟道电流I CH并联的附加电流分量I DS_LK是跨过N漂移区和P基极区之间的pn结的漏电流。晶体管。在这项研究中,研究人员明确指出,由于栅极上没有电压偏置来开启器件,因此没有考虑 SiC JFET 的栅极漏电流。

图 3:SiC JFET(左)和 SiC MOSFET(右)故障模型验证

对于SiC MOSFET的电路仿真,采用基于Shichman-Hodges物理模型的SPICE Level 1模型来描述截止区、线性区和饱和区三种模式,而对于SiC JFET,则采用Shockley物理模型:用过的。通常,在短路事件中,沟道中的电荷载流子受到较高电流应力的影响,并且被加热到相对于正常开关状态更高的温度。因此,沟道载流子的准确迁移率模型对于理解载流子行为对晶体管短路性能的影响非常重要。

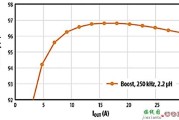

失效模型验证

在短路故障情况下对所开发的 SiC JFET 和 SiC MOSFET 失效模型进行了验证,图中显示了从模型获得的失效电流与论文中的结果的比较。6,7结果表明,在 400V 直流电压下,SiC JFET 的短路故障时间 (tSC) 为 150μs,而在 600V 直流电压下,SiC MOSFET 的短路故障时间 (tSC) 为 13μs。(编者注:图 3 显示了参考文献 24 和 25,在本文中被视为参考文献 6 和 7。)

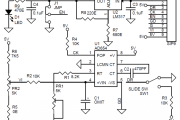

图4:短路事件性能比较示意图

短路故障情况下的验证如图所示,V DC为直流母线电压,R S为电路环路杂散电阻,R G为栅极电阻,DUT 为器件(SiC JFET)或 SiC MOSFET)。图中演示了两种失效模式,红色曲线为第一种失效模式,蓝色曲线为第二种失效模式。注意到的一些参数是SiC JFET的失效时间比SiC MOSFET长得多,并且SiC JFET的饱和电流比SIC MOSFET低。这些变化的原因是载流子迁移率的温度相关系数。

该团队总结道:“对于立即失效,SiC JFET 表现出比 SiC MOSFET 更好的短路能力,并且 SiC JFET 的失效时间和临界失效能量都高于 SiC MOSFET。” “对于延迟失效,在较低的直流母线电压下,SiC JFET 的失效时间比 SiC MOSFET 长得多;然而,对于更高的直流母线电压,两个 SiC 晶体管的故障时间差异似乎很小。”

由于开关速度快和通态电阻低,SiC MOSFET 通常很容易因短路事件而损坏。3安徽工业大学电气与信息工程学院的研究团队提出了两种常用功率器件中 SiC 器件在短路事件中的失效模型:SiC MOSFET(Cree 的 N 沟道增强型 SiC MOSFET) )和 SiC JFET(通常采用英飞凌的 SiC JFET)。4

开发 SiC 晶体管在短路事件中的故障模型

Wang等人提出的论文中研究表明,在短路事件下,故障电流高于功率器件的额定电流。5这意味着漏电流会导致故障电流,为了验证这一点,使用了计算机辅助设计(TCAD)模拟技术。SiC JFET 和 SiC MOSFET 的电流分量描述了两个 SiC 晶体管中的空穴电流密度。分析执行的文件,我们可以得出结论,高密度空穴电流流过晶体管的N漂移区和P基极区之间的pn结。“TCAD仿真还表明,对于SiC MOSFET,高浓度载流子聚集在JFET区域的顶部;其中一小部分注入到栅极氧化物中,在高温和高电场强度的应力下形成栅极漏电流,”该团队解释道。

故障 - 短路事件前 SiC JFET(上)和 SiC MOSFET(下)中空穴电流密度的分布

SiC JFET和 SiC MOSFET失效模型原理图的设计考虑了漏电流的引入。虚线框中的结构是传统电路模型的一部分,与沟道电流I CH并联的附加电流分量I DS_LK是跨过N漂移区和P基极区之间的pn结的漏电流。晶体管。在这项研究中,研究人员明确指出,由于栅极上没有电压偏置来开启器件,因此没有考虑 SiC JFET 的栅极漏电流。

SiC JFET(左)和 SiC MOSFET(右)的失效模型

通过pn结的漏电流的表达式由热产生电流I th、雪崩电流I av和扩散电流I diff组成。然而,对于栅极氧化物中的漏电流,已经提出了几种方法,团队考虑了福勒-诺德海姆(FN)隧道和普尔-弗伦克尔(PF)发射。因此电流 I FN和 I PF被认为对 SiC MOSFET 栅极氧化物的漏电流有贡献。

图 3:SiC JFET(左)和 SiC MOSFET(右)故障模型验证

对于SiC MOSFET的电路仿真,采用基于Shichman-Hodges物理模型的SPICE Level 1模型来描述截止区、线性区和饱和区三种模式,而对于SiC JFET,则采用Shockley物理模型:用过的。通常,在短路事件中,沟道中的电荷载流子受到较高电流应力的影响,并且被加热到相对于正常开关状态更高的温度。因此,沟道载流子的准确迁移率模型对于理解载流子行为对晶体管短路性能的影响非常重要。

失效模型验证

在短路故障情况下对所开发的 SiC JFET 和 SiC MOSFET 失效模型进行了验证,图中显示了从模型获得的失效电流与论文中的结果的比较。6,7结果表明,在 400V 直流电压下,SiC JFET 的短路故障时间 (tSC) 为 150μs,而在 600V 直流电压下,SiC MOSFET 的短路故障时间 (tSC) 为 13μs。(编者注:图 3 显示了参考文献 24 和 25,在本文中被视为参考文献 6 和 7。)

“载流子迁移率取决于温度和电场强度,对于准确开发 SiC 功率器件的故障模型是必要的,”该团队指出。“此外,通过改变I DS_LK的三个电流分量的组合方式,可以得到一个结论性的结果,即I TH决定了所开发的模型是否能够模拟设备的故障。因此,短路期间产生的热电流在故障效应中起着至关重要的作用。”

图4:短路事件性能比较示意图

短路故障情况下的验证如图所示,V DC为直流母线电压,R S为电路环路杂散电阻,R G为栅极电阻,DUT 为器件(SiC JFET)或 SiC MOSFET)。图中演示了两种失效模式,红色曲线为第一种失效模式,蓝色曲线为第二种失效模式。注意到的一些参数是SiC JFET的失效时间比SiC MOSFET长得多,并且SiC JFET的饱和电流比SIC MOSFET低。这些变化的原因是载流子迁移率的温度相关系数。

SiC JFET(左)和 SiC MOSFET(右)的两种故障模式

该团队总结道:“对于立即失效,SiC JFET 表现出比 SiC MOSFET 更好的短路能力,并且 SiC JFET 的失效时间和临界失效能量都高于 SiC MOSFET。” “对于延迟失效,在较低的直流母线电压下,SiC JFET 的失效时间比 SiC MOSFET 长得多;然而,对于更高的直流母线电压,两个 SiC 晶体管的故障时间差异似乎很小。”

相关文章

发表评论