双联开关接线图双联开关接线图双联开关接线图【实战问题】 家用卫生间有个开关,是2个按纽的,一个控制镜前灯,另一个控制吸顶灯,开关呢,是松日的,有 6个...

在设计中使用逐次逼近寄存器 ADC

接线图

2024年01月28日 08:55 218

admin

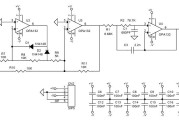

SAR-ADC 的工作原理 SAR-ADC(图 1)捕获模拟电压信号,将该信号转换为数字字。模拟信号通过外部采样/保持设备或 SAR-ADC 的内部采样/保持功能来捕获。SAR-ADC 将此输入电压与转换器外部或内部参考电压 (VREF) 的已知部分进行比较。该参考电压设置转换器的满量程输入电压范围。现代 SAR-ADC 使用电容式数模转换器 (C-DAC) 来连续比较位组合,并将适当的位设置或清除到数据寄存器中。

点击图片可放大。

图 1. 这是现代 SAR-ADC 16 位转换器的内部采样机制模型。在 VS 获取信号后,片选从高电平转变为低电平并打开输入开关 (S1)。

在 SAR 转换器的输入端,输入信号首先经过开关。请注意,闭合开关会产生与电容阵列串联的开关电阻 (RIN)。这些电容器的顶部连接到比较器的反相输入。底侧可以连接到输入电压、参考电压 (VREF) 或接地 (V–)。最初,底侧连接到输入信号 VS。一旦电容阵列完全获取输入信号,输入开关(S1)打开,转换器开始转换过程。

在转换过程中,MSB 电容器的底部连接到 VREF,而其他电容器连接到 V–(或系统接地)。此操作会在所有电容器之间重新分配电荷。比较器的反相输入根据电荷平衡升高或降低电压。如果 SC 处的电压大于 VREF 的一半,转换器会将“0”分配给 MSB 并将该值从串行端口传输出去。如果该电压小于 VREF 的一半,转换器会从串行端口发送“1”,并且转换器将 MSB 电容器连接到 V–。在 MSB 分配之后,对 MSB-1 电容器重复此过程。请注意,图 1 未显示 MSB-1 电容器,但其值为 8C。

SAR-ADC 转换过程所需的时间包括采集时间和转换时间。整个转换过程结束时,SAR-ADC 进入睡眠模式。 驱动您的 SAR-ADC

点击图片可放大。

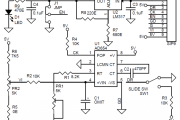

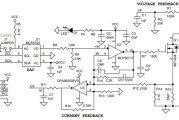

图 2. SAR-ADC 应用设计需要驱动电路(运算放大器、RISO 和 CISO),以确保 ADC 在转换器采集期间具有稳定的输入信号。

在设计 SAR-ADC 电路时,首先确定输入信号的带宽和满量程范围。然后,您选择的 SAR-ADC 应与每个奈奎斯特输入信号的带宽相匹配。该转换器还应该具有适合您的系统的分辨率。在此设计中,关键的 SAR-ADC 规格是电容阵列的累积值、CIN(相当于 SAR-ADC 的输入电容)、转换器满量程输入范围和采集时间 (tAQU)。

现在我们通过确定 RISO 和 CISO 的值??来定义它们。图 3 示波器捕获显示了 SAR-ADC (ADS8326) 的输入电荷注入瞬态。在此测量中,放大器缓冲器和 SAR-ADC (Ch1) 之间有一个 10 kOhm 电阻。启动转换或芯片选择信号出现在顶部曲线 (Ch4) 上。请注意,SAR 转换器的输入阻抗绝不能高达 10 kOhm?但这使我们能够看到 SAR-ADC 输入处的高频电流尖峰。

ADC 基础知识,第 3 部分:在设计中使用逐次逼近寄存器 ADC

图 3. 10 kOhm 电阻器捕获 16 位 SAR-ADC (Ch1) 输入端的电荷注入幅度。CS 引脚会启动每次发生的杂散,该杂散发生在 ADC 采集周期 (Ch4) 期间。

图 3. 10 kOhm 电阻器捕获 16 位 SAR-ADC (Ch1) 输入端的电荷注入幅度。CS 引脚会启动每次发生的杂散,该杂散发生在 ADC 采集周期 (Ch4) 期间。

当转换器采集输入信号时,SAR-ADC 输入端会发生电荷注入。这些高频尖峰给驱动运算放大器带来了非常苛刻的负载。

如图1所示,SAR转换器很少有内置输入缓冲放大器。该电路需要一个具有无失真、轨到轨输入级的运算放大器(请参阅 OPA364 数据表,第 8 页)。该放大器的输出级范围为比正电源低 100 mV 至 100 mV。

RISO 和 CISO(图 2 )的功能是为电荷注入提供一条接地路径,并将运放输出与这些瞬态隔离。RISO 和 CISO 有效地完成了将放大器与容性负载隔离以及吸收来自 SAR-ADC 的电荷尖峰的任务。然而,这两个组件也会修改放大器的开环增益响应,如波特图所示。

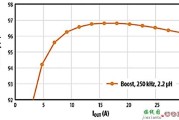

图 4 显示了该系统的运算放大器示例和波特图。查看左侧 y 轴如何绘制放大器的开环和闭环增益。右侧 y 轴绘制了放大器的开环相位响应。x 轴绘制频率。

图 4. RISO|CISO 负载下 OPA364 开环增益/相位与频率的关系。

图 4. RISO|CISO 负载下 OPA364 开环增益/相位与频率的关系。

该放大器 (OPA364) 的开环增益曲线在 10 Hz 时增益为 100 dB。随着频率增加,该增益曲线 (~100 Hz) 变为 –20 dB/十倍频程斜率。该斜率一直持续到曲线继续超过 0 dB。开环增益曲线与 0 dB 交点处的频率为 7 MHz。

当外部电路(RISO|CISO)加载放大器时,开环增益曲线被修改。在图 4 中,蓝色曲线代表修改后的开环曲线。RISO 和 CISO 以及放大器的输出电阻在 fPX 处生成极点,在 fZX 处生成零值。如图 4所示,RISO 和 CISO 的极点出现在 769 kHz 处,零点出现在 1.6 MHz 处。该修改后的开环增益曲线的斜率在 fPX 时从 –20 dB/十倍频程变为 –40 dB/十倍频程,并在 1.6 MHz 处的零 fPZ 时恢复到 –20 dB/十倍频程的斜率。

电路稳定性是在开环增益曲线和闭环增益曲线的交点(3.2 MHz)处定义的。在此交点处,如果这两条曲线的斜率之差为 20 dB/十倍频程,则放大器将稳定。如果这些斜率之间的差异大于 20 dB/十倍频程(例如 40 dB/十倍频程),则放大器电路将稍微稳定。

为了最大限度地减少内部采样电容器的非线性影响,以及最大限度地减少电荷注入对输入电压的影响,最小 CISO 值是内部 SAR-ADC 采样电容器大小的 20 倍。通过注意该 R|C 电路必须在转换器的采集时间内完全稳定来找到 RISO 值。

点击图片可放大。

图 1. 这是现代 SAR-ADC 16 位转换器的内部采样机制模型。在 VS 获取信号后,片选从高电平转变为低电平并打开输入开关 (S1)。

在 SAR 转换器的输入端,输入信号首先经过开关。请注意,闭合开关会产生与电容阵列串联的开关电阻 (RIN)。这些电容器的顶部连接到比较器的反相输入。底侧可以连接到输入电压、参考电压 (VREF) 或接地 (V–)。最初,底侧连接到输入信号 VS。一旦电容阵列完全获取输入信号,输入开关(S1)打开,转换器开始转换过程。

在转换过程中,MSB 电容器的底部连接到 VREF,而其他电容器连接到 V–(或系统接地)。此操作会在所有电容器之间重新分配电荷。比较器的反相输入根据电荷平衡升高或降低电压。如果 SC 处的电压大于 VREF 的一半,转换器会将“0”分配给 MSB 并将该值从串行端口传输出去。如果该电压小于 VREF 的一半,转换器会从串行端口发送“1”,并且转换器将 MSB 电容器连接到 V–。在 MSB 分配之后,对 MSB-1 电容器重复此过程。请注意,图 1 未显示 MSB-1 电容器,但其值为 8C。

SAR-ADC 转换过程所需的时间包括采集时间和转换时间。整个转换过程结束时,SAR-ADC 进入睡眠模式。 驱动您的 SAR-ADC

点击图片可放大。

图 2. SAR-ADC 应用设计需要驱动电路(运算放大器、RISO 和 CISO),以确保 ADC 在转换器采集期间具有稳定的输入信号。

在设计 SAR-ADC 电路时,首先确定输入信号的带宽和满量程范围。然后,您选择的 SAR-ADC 应与每个奈奎斯特输入信号的带宽相匹配。该转换器还应该具有适合您的系统的分辨率。在此设计中,关键的 SAR-ADC 规格是电容阵列的累积值、CIN(相当于 SAR-ADC 的输入电容)、转换器满量程输入范围和采集时间 (tAQU)。

现在我们通过确定 RISO 和 CISO 的值??来定义它们。图 3 示波器捕获显示了 SAR-ADC (ADS8326) 的输入电荷注入瞬态。在此测量中,放大器缓冲器和 SAR-ADC (Ch1) 之间有一个 10 kOhm 电阻。启动转换或芯片选择信号出现在顶部曲线 (Ch4) 上。请注意,SAR 转换器的输入阻抗绝不能高达 10 kOhm?但这使我们能够看到 SAR-ADC 输入处的高频电流尖峰。

ADC 基础知识,第 3 部分:在设计中使用逐次逼近寄存器 ADC

图 3. 10 kOhm 电阻器捕获 16 位 SAR-ADC (Ch1) 输入端的电荷注入幅度。CS 引脚会启动每次发生的杂散,该杂散发生在 ADC 采集周期 (Ch4) 期间。

图 3. 10 kOhm 电阻器捕获 16 位 SAR-ADC (Ch1) 输入端的电荷注入幅度。CS 引脚会启动每次发生的杂散,该杂散发生在 ADC 采集周期 (Ch4) 期间。当转换器采集输入信号时,SAR-ADC 输入端会发生电荷注入。这些高频尖峰给驱动运算放大器带来了非常苛刻的负载。

如图1所示,SAR转换器很少有内置输入缓冲放大器。该电路需要一个具有无失真、轨到轨输入级的运算放大器(请参阅 OPA364 数据表,第 8 页)。该放大器的输出级范围为比正电源低 100 mV 至 100 mV。

RISO 和 CISO(图 2 )的功能是为电荷注入提供一条接地路径,并将运放输出与这些瞬态隔离。RISO 和 CISO 有效地完成了将放大器与容性负载隔离以及吸收来自 SAR-ADC 的电荷尖峰的任务。然而,这两个组件也会修改放大器的开环增益响应,如波特图所示。

图 4 显示了该系统的运算放大器示例和波特图。查看左侧 y 轴如何绘制放大器的开环和闭环增益。右侧 y 轴绘制了放大器的开环相位响应。x 轴绘制频率。

图 4. RISO|CISO 负载下 OPA364 开环增益/相位与频率的关系。

图 4. RISO|CISO 负载下 OPA364 开环增益/相位与频率的关系。该放大器 (OPA364) 的开环增益曲线在 10 Hz 时增益为 100 dB。随着频率增加,该增益曲线 (~100 Hz) 变为 –20 dB/十倍频程斜率。该斜率一直持续到曲线继续超过 0 dB。开环增益曲线与 0 dB 交点处的频率为 7 MHz。

当外部电路(RISO|CISO)加载放大器时,开环增益曲线被修改。在图 4 中,蓝色曲线代表修改后的开环曲线。RISO 和 CISO 以及放大器的输出电阻在 fPX 处生成极点,在 fZX 处生成零值。如图 4所示,RISO 和 CISO 的极点出现在 769 kHz 处,零点出现在 1.6 MHz 处。该修改后的开环增益曲线的斜率在 fPX 时从 –20 dB/十倍频程变为 –40 dB/十倍频程,并在 1.6 MHz 处的零 fPZ 时恢复到 –20 dB/十倍频程的斜率。

电路稳定性是在开环增益曲线和闭环增益曲线的交点(3.2 MHz)处定义的。在此交点处,如果这两条曲线的斜率之差为 20 dB/十倍频程,则放大器将稳定。如果这些斜率之间的差异大于 20 dB/十倍频程(例如 40 dB/十倍频程),则放大器电路将稍微稳定。

为了最大限度地减少内部采样电容器的非线性影响,以及最大限度地减少电荷注入对输入电压的影响,最小 CISO 值是内部 SAR-ADC 采样电容器大小的 20 倍。通过注意该 R|C 电路必须在转换器的采集时间内完全稳定来找到 RISO 值。

相关文章

发表评论