双联开关接线图双联开关接线图双联开关接线图【实战问题】 家用卫生间有个开关,是2个按纽的,一个控制镜前灯,另一个控制吸顶灯,开关呢,是松日的,有 6个...

USB 3.0 环境的信号完整性

接线图

2024年02月20日 21:07 217

admin

在处理新的 SuperSpeed USB 3.0 标准时,保持高速信号的完整性是最大的挑战之一。信号转接驱动器可以增强和均衡信号,而多路复用器可以最大限度地减少端口远离主机控制器的系统的性能下降。其结果是一个灵活、可靠的 USB 3.0 系统,可保持信号完整性。

USB 在全球的安装量超过 60 亿台,几乎 100% 存在于所有 PC 和外围设备中,是无可争议的接口之王。运行速度为 480 Mbps 的高速 USB 2.0 在过去十年中已经满足了大多数消费者的需求,但现在,随着高清视频成为常态,人们渴望更快地下载数字内容,是时候进行升级了。

新规范 SuperSpeed USB 3.0 的带宽足足增加了 10 倍,通过双绞线电缆的运行速度高达 5 Gbps。新规范向后兼容 USB 2.0,但现实是 USB 3.0 是另一种动物。USB 2.0 使用简单的基于总线的架构以及监督操作的主机,而 USB 3.0 使用更复杂的差分信号技术,包括端口定向、分组环境中的双向连接。

对于具有其他高速串行接口(例如第二代和第三代 PCI Express)经验的工程师来说,从 USB 2.0 过渡到 USB 3.0 将更容易,因为这些协议与 USB 3.0 非常相似,尤其是在物理层。但只有 USB 2.0 经验的工程师在开始处理 USB 3.0 的多千兆位信号速率时可能会面临学习曲线。与任何高速接口一样,USB 3.0 面临的最大挑战之一是信号完整性。

随着信号速度的提高,信号质量会迅速下降,尤其是当传输涉及长 PCB 走线、多个连接器和不同长度的电缆时。

为了帮助提高高速信号完整性,恩智浦开发了可增强和均衡信号的转接驱动器,以及可最大限度减少端口远离主机控制器的系统中的信号衰减的多路复用器。在本文中,我们介绍 PTN36241B 和 PTN36242L 转接驱动器以及 CBTL02042A/B 和 CBTL02043A/B 多路复用器,并了解它们如何帮助设计人员创建符合 USB 合规标准的可靠、灵活的 USB 3.0 系统。

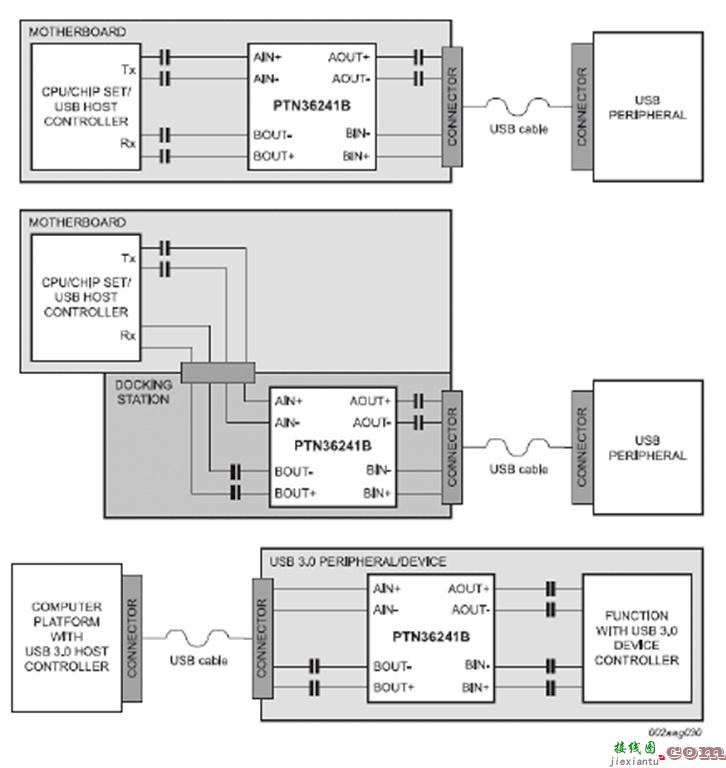

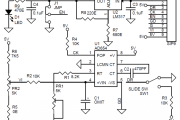

PTN36241B 和 PTN36242L 转接驱动器 USB 3.0 控制器现已集成到距离 USB 端口一定距离的芯片组中。如果控制器和端口连接器之间的 PCB 走线太长,信号将迅速衰减。信号转接驱动器可以增强信号,使其在到达端口所需的距离时保持其完整性。 通过电缆传输也会出现类似的信号完整性问题。USB 3.0 可能比 USB 2.0 快十倍,但最大电缆长度更短。使用 USB 2.0,信号传输至少五米,但使用 USB 3.0,标准电缆限制仅为三米。这里也可以使用信号转接驱动器,以在更长的距离上传输信号。通过设计在电缆延长器中的转接驱动器,USB 3.0 信号可以可靠地传输七米或更远。NXP 开发了两款适用于 USB 3.0 的转接驱动器:单端口 PTN36241B 和双端口 PTN3624L。这两款器件均可在一系列 USB 3.0 环境中提供业界领先的信号完整性。图 1 显示了单端口 PTN36241B 的示例配置。双端口 PTN3624L 可用于类似的配置, 图 1 单端口 PTN36241B USB 3.0 转接驱动器的示例应用

图 1 单端口 PTN36241B USB 3.0 转接驱动器的示例应用

两款 NXP 转接驱动器均通过两个通道支持 5 Gbps。一个通道的数据流面向 USB 主机,而另一通道面向 USB 外设或设备。每个通道均包含一个 SuperSpeed 发送 (Tx) 差分通道和一个 SuperSpeed (Rx) 差分通道。在大多数情况下,这种配置允许设计人员将系统从 USB 2.0 过渡到 USB 3.0,而无需更改外形尺寸或 PCB 材料 (FR4),从而以快速、廉价的方式交付新的向后兼容系统。引脚排列还可以将走线路由与 USB 3.0 连接器相匹配。每个转接驱动器都会调节 USB 3.0 信号,以便传输更远的距离。该设备对恶化的输入信号执行接收均衡,然后以去加重的方式发送信号,以最大限度地提高系统链路性能。这两款器件都配备了多个配置引脚(PTN36241B 有五个级别,PTN36242L 有四个级别),因此每个通道都可以选择接收器均衡、发送器去加重和输出摆幅级别。每个通道上具有可选的发送去加重和输出摆幅,可提供适合特定通道条件的信号预补偿。集成终端电阻在发送和接收路径上提供阻抗匹配,并且自动指示和检测接收器终端。PTN36241B 在五级配置引脚上提供 I2C 总线接口的智能复用。默认情况下,该器件配置有板载级别的配置引脚。当通过这些复用引脚执行 I 2C 总线读/写操作时,该器件对每个 I 2C 事务进行解码并相应地配置其内部功能。内置电源管理功能可通过各种 USB 3.0 低功耗模式 (U2/U3) 显着节省功耗。该器件检测 LFPS 信令和链路的电气状况,并可以动态激活或停用内部电路和逻辑。该器件无需主机软件干预即可执行这些操作并节省电量。每个转接驱动器都支持自动兼容技术,可实现由内部状态机控制的一致性测试,从而无需单独的硬件一致性引脚。两个转接驱动器均由 3.3 V 电源供电。单端口 PTN36241B 采用 HVQFN24 封装(4 x 4 x 1 mm,0.5 mm 间距),双端口 PTN36242L 采用 HVQFN32 封装(3 x 6 x 0.85 mm,0.5 mm)。

CBTL02042A/B 和 CBTL02043A/B 开关

CBTL02042A/B 和 CBTL02043A/B 专为高速串行接口应用而设计,是具有两个差分通道的 2 对 1 多路复用器/解复用器开关。它们用于将两个差分信号切换到信号衰减较低的两个位置之一。CBTL02042A/B 支持高达 7 GHz 的带宽,CBTL02043A/B 是业界首款支持高达 10 GHz 带宽的交换机。图 2 给出了一个示例应用程序,其中 CBTL02042A 用于在笔记本电脑的主主板和扩展坞之间进行复用。

屏幕截图 2012-10-02 下午 3.36.00.png

图 2 CBTL02042A 可以在笔记本电脑主板和扩展坞之间进行复用

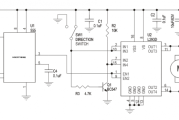

恩智浦的高带宽 CMOS 传输门技术最大限度地降低了开关阻抗,并允许扩展现有的高速端口,从而有助于提高带宽和降低插入损耗。独特的设计技术最大限度地降低了开关的阻抗,使得通过开关观察到的衰减可以忽略不计。该技术还最大限度地减少了高速接口所要求的通道间偏移和通道间串扰。因此,这两款器件都具有极低的插入损耗:100 MHz 时为 -0.5 dB,4.0 GHz 时为 -1.3 dB。图 3 给出了 CBTL02043A/B 的差分插入损耗行为。

屏幕截图 2012-10-02 下午 3.36.11.png

图3 CBTL02043A开关的差分插损

这两款器件均设计用于扩展现有的高速端口,以实现极低的功耗。每个都配备了关闭功能,以最大限度地减少应用程序不活动时的功耗。待机电流消耗小于 1 ?A。这两款器件均采用紧凑型 DHVQFN20 封装,并提供不同的引脚排列以支持特定的应用布局。“A”版本使用“流通”引脚排列,在封装的相对两侧具有输入和输出引脚。它们非常适合与主板上具有不同信号源的边缘连接器一起使用,以及信号传播变化且走线长度不那么重要的情况。“B”版本使用“环绕式”引脚排列,并且在封装的两侧都有输出。

USB 在全球的安装量超过 60 亿台,几乎 100% 存在于所有 PC 和外围设备中,是无可争议的接口之王。运行速度为 480 Mbps 的高速 USB 2.0 在过去十年中已经满足了大多数消费者的需求,但现在,随着高清视频成为常态,人们渴望更快地下载数字内容,是时候进行升级了。

新规范 SuperSpeed USB 3.0 的带宽足足增加了 10 倍,通过双绞线电缆的运行速度高达 5 Gbps。新规范向后兼容 USB 2.0,但现实是 USB 3.0 是另一种动物。USB 2.0 使用简单的基于总线的架构以及监督操作的主机,而 USB 3.0 使用更复杂的差分信号技术,包括端口定向、分组环境中的双向连接。

对于具有其他高速串行接口(例如第二代和第三代 PCI Express)经验的工程师来说,从 USB 2.0 过渡到 USB 3.0 将更容易,因为这些协议与 USB 3.0 非常相似,尤其是在物理层。但只有 USB 2.0 经验的工程师在开始处理 USB 3.0 的多千兆位信号速率时可能会面临学习曲线。与任何高速接口一样,USB 3.0 面临的最大挑战之一是信号完整性。

随着信号速度的提高,信号质量会迅速下降,尤其是当传输涉及长 PCB 走线、多个连接器和不同长度的电缆时。

为了帮助提高高速信号完整性,恩智浦开发了可增强和均衡信号的转接驱动器,以及可最大限度减少端口远离主机控制器的系统中的信号衰减的多路复用器。在本文中,我们介绍 PTN36241B 和 PTN36242L 转接驱动器以及 CBTL02042A/B 和 CBTL02043A/B 多路复用器,并了解它们如何帮助设计人员创建符合 USB 合规标准的可靠、灵活的 USB 3.0 系统。

PTN36241B 和 PTN36242L 转接驱动器 USB 3.0 控制器现已集成到距离 USB 端口一定距离的芯片组中。如果控制器和端口连接器之间的 PCB 走线太长,信号将迅速衰减。信号转接驱动器可以增强信号,使其在到达端口所需的距离时保持其完整性。 通过电缆传输也会出现类似的信号完整性问题。USB 3.0 可能比 USB 2.0 快十倍,但最大电缆长度更短。使用 USB 2.0,信号传输至少五米,但使用 USB 3.0,标准电缆限制仅为三米。这里也可以使用信号转接驱动器,以在更长的距离上传输信号。通过设计在电缆延长器中的转接驱动器,USB 3.0 信号可以可靠地传输七米或更远。NXP 开发了两款适用于 USB 3.0 的转接驱动器:单端口 PTN36241B 和双端口 PTN3624L。这两款器件均可在一系列 USB 3.0 环境中提供业界领先的信号完整性。图 1 显示了单端口 PTN36241B 的示例配置。双端口 PTN3624L 可用于类似的配置,

图 1 单端口 PTN36241B USB 3.0 转接驱动器的示例应用

图 1 单端口 PTN36241B USB 3.0 转接驱动器的示例应用两款 NXP 转接驱动器均通过两个通道支持 5 Gbps。一个通道的数据流面向 USB 主机,而另一通道面向 USB 外设或设备。每个通道均包含一个 SuperSpeed 发送 (Tx) 差分通道和一个 SuperSpeed (Rx) 差分通道。在大多数情况下,这种配置允许设计人员将系统从 USB 2.0 过渡到 USB 3.0,而无需更改外形尺寸或 PCB 材料 (FR4),从而以快速、廉价的方式交付新的向后兼容系统。引脚排列还可以将走线路由与 USB 3.0 连接器相匹配。每个转接驱动器都会调节 USB 3.0 信号,以便传输更远的距离。该设备对恶化的输入信号执行接收均衡,然后以去加重的方式发送信号,以最大限度地提高系统链路性能。这两款器件都配备了多个配置引脚(PTN36241B 有五个级别,PTN36242L 有四个级别),因此每个通道都可以选择接收器均衡、发送器去加重和输出摆幅级别。每个通道上具有可选的发送去加重和输出摆幅,可提供适合特定通道条件的信号预补偿。集成终端电阻在发送和接收路径上提供阻抗匹配,并且自动指示和检测接收器终端。PTN36241B 在五级配置引脚上提供 I2C 总线接口的智能复用。默认情况下,该器件配置有板载级别的配置引脚。当通过这些复用引脚执行 I 2C 总线读/写操作时,该器件对每个 I 2C 事务进行解码并相应地配置其内部功能。内置电源管理功能可通过各种 USB 3.0 低功耗模式 (U2/U3) 显着节省功耗。该器件检测 LFPS 信令和链路的电气状况,并可以动态激活或停用内部电路和逻辑。该器件无需主机软件干预即可执行这些操作并节省电量。每个转接驱动器都支持自动兼容技术,可实现由内部状态机控制的一致性测试,从而无需单独的硬件一致性引脚。两个转接驱动器均由 3.3 V 电源供电。单端口 PTN36241B 采用 HVQFN24 封装(4 x 4 x 1 mm,0.5 mm 间距),双端口 PTN36242L 采用 HVQFN32 封装(3 x 6 x 0.85 mm,0.5 mm)。

CBTL02042A/B 和 CBTL02043A/B 开关

CBTL02042A/B 和 CBTL02043A/B 专为高速串行接口应用而设计,是具有两个差分通道的 2 对 1 多路复用器/解复用器开关。它们用于将两个差分信号切换到信号衰减较低的两个位置之一。CBTL02042A/B 支持高达 7 GHz 的带宽,CBTL02043A/B 是业界首款支持高达 10 GHz 带宽的交换机。图 2 给出了一个示例应用程序,其中 CBTL02042A 用于在笔记本电脑的主主板和扩展坞之间进行复用。

屏幕截图 2012-10-02 下午 3.36.00.png

图 2 CBTL02042A 可以在笔记本电脑主板和扩展坞之间进行复用

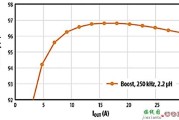

恩智浦的高带宽 CMOS 传输门技术最大限度地降低了开关阻抗,并允许扩展现有的高速端口,从而有助于提高带宽和降低插入损耗。独特的设计技术最大限度地降低了开关的阻抗,使得通过开关观察到的衰减可以忽略不计。该技术还最大限度地减少了高速接口所要求的通道间偏移和通道间串扰。因此,这两款器件都具有极低的插入损耗:100 MHz 时为 -0.5 dB,4.0 GHz 时为 -1.3 dB。图 3 给出了 CBTL02043A/B 的差分插入损耗行为。

屏幕截图 2012-10-02 下午 3.36.11.png

图3 CBTL02043A开关的差分插损

这两款器件均设计用于扩展现有的高速端口,以实现极低的功耗。每个都配备了关闭功能,以最大限度地减少应用程序不活动时的功耗。待机电流消耗小于 1 ?A。这两款器件均采用紧凑型 DHVQFN20 封装,并提供不同的引脚排列以支持特定的应用布局。“A”版本使用“流通”引脚排列,在封装的相对两侧具有输入和输出引脚。它们非常适合与主板上具有不同信号源的边缘连接器一起使用,以及信号传播变化且走线长度不那么重要的情况。“B”版本使用“环绕式”引脚排列,并且在封装的两侧都有输出。

相关文章

发表评论