开漏、开集电路详解-电路图讲解-电子技术方案

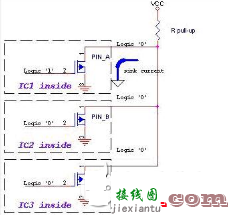

在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。这两个概念到底是什么呢?下文给你带来详细介绍。 开漏(opendrain)介绍 开漏电路概念中提到的“漏”就是指MOSFET的漏极。同理,开集电路中的“集”就是指三极管的集电极。开漏电路就是指以MOSFET的漏极为输出的电路。 所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。同理,开集电路中的“集”就是指三极管的集电极。开漏电路就是指以MOSFET的漏极为输出的电路。一般的用法是会在漏极外部的电路添加上拉电阻。完整的开漏电路应该由开漏器件和开漏上拉电阻组成。如下图所示:

组成开漏形式的电路特点 1.利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经Rpull-up,MOSFET到GND。IC内部仅需很小的栅极驱动电流。

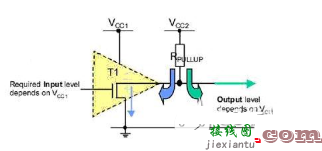

2.可以将多个开漏输出的Pin,连接到一条线上。形成“与逻辑”关系。如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。 3.可以利用改变上拉电源的电压,改变传输电平。IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。 4.开漏Pin不连接外部的上拉电阻,则只能输出低电平。 5.标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。 开集(opencollector)介绍 Open-collector/ Open-drain是用于多个device间使用一个连接线来双向(Bi-direcTIonally)通信的技术。 如图所示

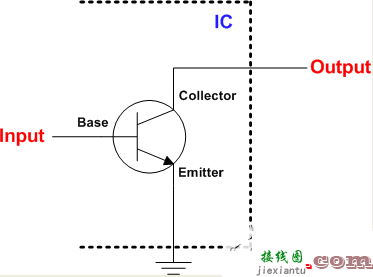

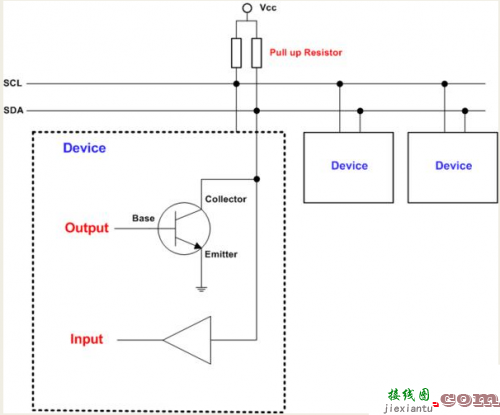

因为Collector的pin没有和任何其他device连接所以叫Open Collector。BJT的情况叫做Open-Collector,MOSFET的情况叫做Open-drain。理论上BJT和MOSFET一样。 在input有high信号的话,transiSTor则为ON,此时Output和Groud形成通路使得Output输出为Low 在input有low信号的话,transistor则为OFF,此时Output为Hi-inpedence状态。 Hi-impedence的意思是阻抗很高,Low和High不能区别的状态。 所以一般情况下,Output会连接有一个Pull-up电阻,在input为low时,能把output的状态从Hi-impedence拉到High状态。 若是在bus线上有多个同样的Open-collector时,只要有一个open-collector的input为low,导致output为low,则引起bus上的状态为low。

这样的bus线叫做wired-OR。

Open-collector因为Pull-up电阻,导致input为low时,output为High。在多个device间不会引起信号冲突。而不使用open-collector的话,多个device发送low或者high时,会引起短路。

开集(Open-collector)的特点

1. 多个device连接时,可以双方向传输(wire-OR)

2. Level不同的device之间也可以传输数据(5V的master可以给3V的slave传输数据)

I2C就是使用此方法构造的。

I2C最初的操作就是发送一个slave address。发送后等待回应ACK

这时多个device中符合其slave地址的device会使其output为low来回应master,使得master判定此device为自己需要交换数据的device。

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选项替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

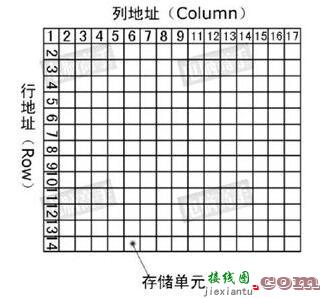

介绍SDRAM电路设计之前先了解下SDRAM的寻址原理。SDRAM内部是一个存储阵列,可以把它想象成一个表格,和表格的检索原理一样,先指定行,再指定列,就可以准确找到所需要的存储单元,这是内存芯片寻址的基本原理,这个表格称为逻辑Bank。由于技术、成本等原因,不可能只做一个全容量的Bank,而且由于SDRAM工作原理限制,单一的Bank会造成非常严重的寻址冲突,大幅降低内存效率,所以在SDRAM内部分割成多个Bank,目前的SDRAM基本都是4个Bank。存储阵列示意如图1所示:

图1 SDRAM存储阵列示意图

图1 SDRAM存储阵列示意图

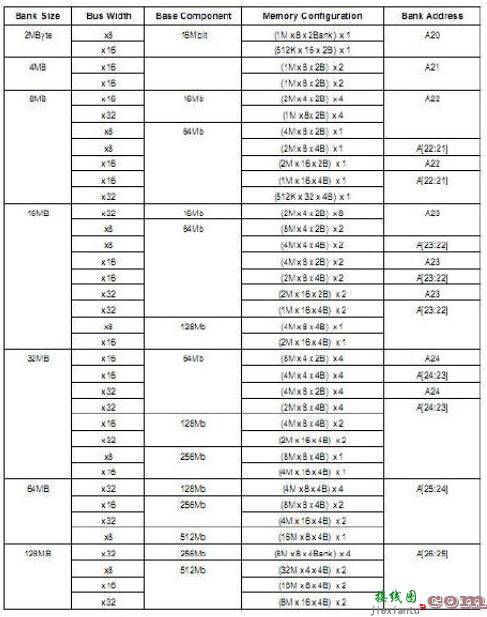

图2 SDRAM引脚配置方案 图2是S3C2440A手册提供的SDRAM bank地址的配置方案,维护系统使用的SDRAM是HY57V561620FTP-H,它的规格是4*4M*16bit(使用两片是为了配置成32位的总线宽度),BANK大小是4M*16=64MB,总线宽度是32位,器件大小是4*BANK大小=256Mb,寄存器配置就是(4M*16*4B)*2,根据图2可知,SDRAM上的BANK地址引脚(BA[1:0])与S3C2440的A[25:24]相连。

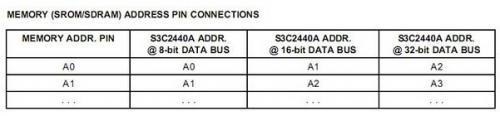

图3 S3C2440A控制地址总线连接

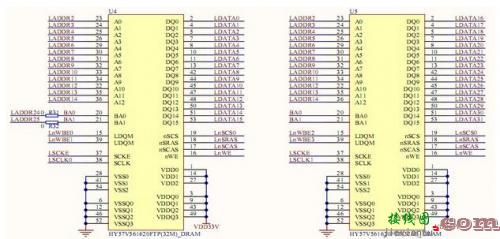

图3是寄存器控制地址总线连接方式,我们使用2片SDRAM配置成32位的总线宽度,所以SDRAM上的A[12:0]接到S3C2440的A[14:2]引脚。具体的SDRAM电路连接如图4所示:

图4 SDRAM电路连接图 SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写地址分两次输入到芯片中,每一次由同一组地址线送入,两次送入到芯片上去的地址分别称为行地址和列地址,它们被锁存到芯片内部的行地址锁存器和列地址锁存器。下面是该芯片的部分信号说明: nSRAS:SDRAM行地址选通信号 nSCAS:SDRAM列地址选通信号 nSCS:SDRAM芯片选择信号(选用Bank6作为sDRAM空间,也可以选择Bank7) nWBE[3:0]:SDRAM数据屏蔽信号 SCLK0[1]:SDRAM时钟信号 SCKE:SDRAM时钟允许信号 LDATA[0:31]:32位数据信号 LADDR[2:14]:行列地址线 LADDR[25:24]:bank选择线

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选项替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

相关文章

发表评论