TCL王牌LCD3026彩电主要信号流程分析

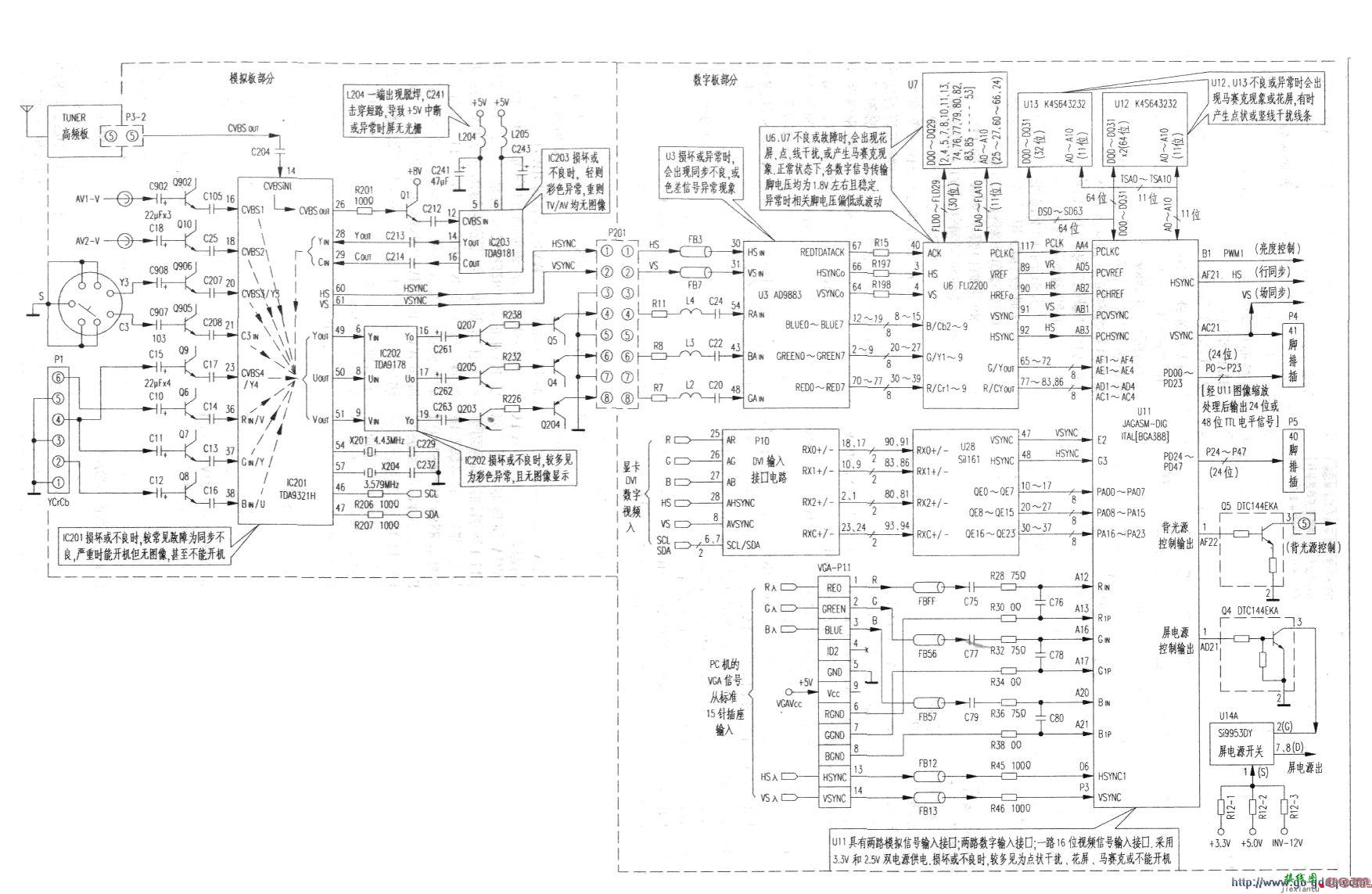

1.视频电路信号流程(见下图)

高频部分主要由高频头TUNER等组成高频板。其内部含有普通数字高频头功能及多制式图像伴音中频解调动能,能直接进行图像中频和伴音中频的处理,输出复合视频电视信号和解调届的伴音音频信号。同时,高频头也可输出第二伴音中频信号SIF并提供给带有丽音解码的机型使用。该高频头采用单一的+5v供电,内含DC/DC转换器,可把+5v变为高频头所需要的33V调谐电压。它具有集成度高、电性能好、体积小、重量轻等优点,应用于LCD彩电上既可减小体积和重量;又可简化线路设计和成本,能有效地提高TV的接收性能及可靠性。

由图1流程图可见,经高频接收并处理后的复合视频信号从高频板的(5)脚输出,通过接插件P3-2(5)脚送至模拟电路板,由耦合电容C204将视频TV-CVBS信号送到IC201(TDA9321H)(14)脚。IC201是一块由IIc总线控制的TV信号输入处理电路,其主要功能是配置有PLL(锁相环)解调器的多制式图像中频电路;IC内设有QSS-IF伴音中频和调幅AM音频解调器;具有可切换的群时延校正电路,可用以补偿B/G群时延的预校正:用IIC总线来控制几种输出的切换,并可以切换外部电路,如声陷波器等。从IC201(14)脚输入的CVBS视频信号进入lC内的视频开关及控制电路,经开关选择和控制处理后,从(26)脚输出,将该信号送至梳状滤波器及Y,C分离电路IC203(TDA9181)(12)脚。在IC201(26)脚与IC203(12)脚之间的视频信号传输电路中,接有Ql(BC847)缓冲放大级,使输出的CVBS信号经缓冲放大后,从IC203(12)脚输入至TDA9181内部进行Y/C分离。

TDA9181是高度集成电路,外围所需元件少,供电为5v.标准损耗电流为35mA.为能自适应PAL/NTSC制式的梳状滤波,内置有两个2H/1H延迟线路,并能确保最佳的交扰亮度和交扰色彩的衰减,同时通过良好的S/N无线电波提供宽广的带宽范围。经IC203分离出来的Y和C信号分别从(14)脚(Y/Vout)、(16)脚(Cout)输出,并分别经C213、C214耦合至IC201的(28)脚(COMBY)、(29)脚(COMBC),送入IC内进行视频解码处理。

在lC内经ACC自动色度控制电路、钟形滤波电路、滤波调整电路、SECAM解调器电路、PAL/NTSC/SECAM转换开关电路、基带延迟电路和Y-开关及陷波、Y-延迟、Y/U/V开关等相关电路处理与运作后,最后分别从(49)、(50)、(51)脚输出YUV分量视频信号至TDA9178(IC202)内部进行画质改善和处理。从IC202(6)、(8)、(9)脚分别输入的YUV信号经内部的亮度、色度矢量处理,黑电平延伸,直方图处理.Y校正和饱和度校正、肤色校正及频谱处理等相关电路处理运作后,分别从(16)、(17)、(19)脚输出YUV信号,在IC202(16)、(17)、(19)脚处,分别由Q207、Q5,Q205、Q4,Q203、Q204组成各自信号的两级缓冲放大器缓冲后,从接口插件P201(4)、(6)、(8)脚输送至数字板。与此同时,IC201(TDA9321H)分离出的行、场同步信号也分别从(60)脚(HACLP)和(61)脚(VA)输出,经接插件P201的(1)、(2)脚送人到数字板电路。从模拟电路板送人数字板的YUV三路模拟色差分量信号,分别经由R11、LA、C24;R8、L3、C22和R7、L2、C20等组成的阻抗匹配和低通滤波电路后,去除高频干扰,分别从AD9883(U3)(48)、(43)和(54)脚进入AD9883内部电路。

AD9883是专为平板显示模拟前端接口而设计的模数转换集成电路,采用80脚LQFP封装和单一的3.3V电压供电,内置三通道8位140MHz采样频率A/D转换器,可输出4:2:2标准的数字视频格式。上述输入的YUV信号经AD9883内部三通道AD转换器转换处理后,分别从U3的(2)-(9)脚(RP3端口)、(12)-(19)脚(RP1端口)和(70)一(77)脚(RP5端口)输出4:2:2格式的YUV数字视频信号。同时,行同步信号(HSYNC)和场同步信号(VSYNC)分别从AD9883(30)脚和(31)脚输入,在IC内部PLL环路控制后,产生内部工作所需的时钟信号及与输出数据信号相对应的数据同步时钟信号(U3(37)脚)、行同步信号(U3(66)脚)和场同步信号(U3(64)脚:VSout)。

AD9883输出的数字格式YUV信号及行、场同步信号分别从FLI2200(U6)的(20)-(27)脚(Y分量信号输入)、(80)-(15)脚(U分量信号输入)、(30)-(39)脚(v分量信号输入)、(40)、(4)脚(数据同步信号与场同步信号输入)、(3)脚(行同步信号输入)输入。FLI2200(U6)是数字视频去隔行处理集成电路.IC内含多种画质改善功能电路,可支持525行60Hz的NTSC或625行的50HzPA/SECAM制式信号输入,可自动检测输入视频信号的制式,支持多种逐行输出数据格式(8,10/16/20位YUV或24/30位YPbPr/RGBHV).内含SDRAM控制器(可在外部连接2Mx32bitSDRAM),内置两组I2C总线接口,内置时钟发生器及显示时序发生器等功能部件。

FLI2200在从复合视频信号输入到产出高质量的图像输出信号过程中起着很大的作用,即去隔行处理。输入的视频信号通过FLI2200(U6)的内部SDRAM接口与外挂的帧缓冲存储器K4S643232C(U7)相连接。经U6内部逐行转换、画质改善、运动补偿及边缘平滑等处理后,从U6(65)-(72)脚和(77)-(86)脚输出16位数据格式的逐行YUV数字信号.U6(89)-(92)脚和(117)脚输出相对应的各种同步时钟信号,其中(91)、(92)脚分别为场、行同步信号输出。

从U6(FLI2200)(65)-(72)、(77)-(86)脚输出的16位YUV数字信号送至Ul1(AF)~(AF4)、(AE1)~(AE4)、(AD1)一(AD4)和(AC1)一(AC4)脚;(91)、(92)脚输出的场、行同步信号分别输入至UI1的(AB1)和(AB4)脚;其余的时钟信号送至U11的相应脚。

U11[JAGASM(BGA388)]是一款集成度相当高且功能强大的平板电视图像处理芯片。它采用388脚塑封形式.3.3V和2.5V双电源供电。

内部集成有功能强大的平板图像缩放处理器(SCALER)、5路独立的输入前端(2路模拟输入接口、2路数字输入接口、一路16位视频信号输入接口)、3通道8位135MHzADC、SDRAM控制器、PLL时钟控制器及一些画质改善、增强等功能电路。U11内置一个SDRAM接口,可与标准的SDRAM芯片实现无缝连接。本机中.Ull与U12和U13两片容量为2Mx32bit的SDRAM芯片(K4S643232Cx2)并联连接,构成2Mx64bit结构,容量为16MB的数据RAM供图像数据处理及帧数据缓冲使用。

Ull在主CPUU19(80C32)的控制下从各个接口输入的信号中选择出一路信号进行处理。当选择的信号为YUV信号时,经U6处理后的16位YUV数字信号和各种同步时钟信号,从UIIA的PORTC端口(AF1—AF4、AE1—AE4、ADl~AD4、AC1—AC4)输入,送到内置的LCD图像处理器中进行处理,处理项目主要包括画质处理、格式变换、大小缩放、时序变换等。同时,选择的输入信号通过Ull内部的SDRAM接口与外挂的帧存储器U12、U13进行数据交换,以显示不同格式的数据。

UI1内置一个独立的16位视频信号输入接口,可提供与视频解码器输出或MPEG2解码器输出等标准输出视频格式的直接连接。在本机中,视频信号输入接口连接的正是FLI2200输出的经过去隔行处理后的标准16位逐行格式视频信号VYO_VY7和VCO~VC7。

经Ull内部一系列处理后,数字视频信号被变换为符合LCD平板显示的数据格式及时序,从Ull的平板显示接口输出48位(或36位,24位、18位,具体的位数视LCD平板模块的输入接口而定,由CPU控制Ull进行选择)平板显示数据和4同步控制信号。Ull输出的24位平板显示数据及4路同步信号送入U15(SN75LVDS83)进行格式转换,U15采用TI公司生产的SN75LVDS83平板连接发送器芯片,采用56脚TSOP封装形式和3.3V单电源供电,时钟频率为31MHz~68MHz。经转换后的4路LVDS信号分别从U15(附图中未画出)的(47)脚(YOP)、(48)脚(YOM)、(45)脚(YIP)、(46)脚(YIM)、(41)脚(Y2P)、(42)脚(Y2M)、(37)脚(Y3P)、(38)脚(Y3M)、(39)脚(CLKOUTP)和(40)脚(CLKOUTM),再经(20)脚接插件接转(CNl)后输出到显示屏进行显示处理。

2.其他外部视频信号输入流程

若在其他状态下工作时,AV1的视频信号从IC201(TDA9321H)(16)脚经Q902缓冲放大后输入CVBSinl信号:AV2的视频信号经C18耦合、010缓冲后从IC201(18)脚(CVBSin2)输入;从(18)脚输入的是自测试图像视频信号,在同类机型中,有的机器未使用,按空脚处理。“S”端子的“CVBS3”或亮度信号“Y3”经0906缓冲后,由C207耦合输入IC201(20)脚,彩色信号“C3”经Q905缓冲后,从(21)脚输入。YCrCb的视频信号分别经接插件Pl(2)、(4)、(6)脚接转后,由相应的耦合电容耦合至Q9、Q6、Q7、Q8,经缓冲放大后分别从(23)、(36)、(37)、(38)脚输入,其中(23)脚输入CVBS4/Y4信号;(36)脚输入Rv信号;(37)脚输入G/Y信号;(38)脚输入B/U信号。以上视频信号输至IC201.经IC内部视频输入选择开关选择后,送至视频解码单元电路作处理。

3.VGA视频信号输入流程

VGA视频信号接口处理主要是PC机(家用电脑)输出的标准VGA信号,其中包括模拟和数字VCA信号(即DVI信号)。

(1)模拟VGA视频信号。该信号主要由Ull (JAG ASM-BGA388)芯片的模拟接口部分及外围相应元件组成。Ull可以和模拟信号的输入设备直接连接,其提供的两路模拟输入接口可同时输入两路模拟VGA信号。本机只使用了一路模拟接口来连接一路模拟VGA信号输入。由图l可见,从标准15针VGA接口(DB15)进来的RGB三路模拟视频信号经PLL接插件和相应的阻抗匹配元件及低通滤波后,分别从UI1的模拟信号接口(A12)、(A13)、(A16)、(A17)、(A20)、(A21)脚输入到U11内部,经IC内的AD转换器转换为24位数字RGB信号后,再送入JAGASM-BCA388内部的LCD图像处理器进行相应的处理。与此同时,VGA信号的行、场同步信号也同时输至UI1的(D6)和(P3)脚内部相应电路。经处理后的VGA信号后续处理过程与YUV信号的运作过程相同。不再赘述。

(2)数字VGA信号,其接口为可选部分,在有DVI输入接口电路的机型中才设置有此项功能。在本机中,数字VGA接口部分主要由DVI接收芯片S11161(U28)、Ull的数字接口部分及相关外围元件组成。Si1161是SILicon Image公司生产的平板连接数字接收器,可支持VCA到UXGA(可选带宽25MHz~162MHz),兼容DVIl.0接口标准,支持24位16.7M真彩色,支持l像素,时钟或2像素,时钟24位或48位输出格式。

S11161采用100脚TQFP封装形式和单一的3.3V供电。由图1可见,从DVI接口Pl0接人的低压差分信号送至TMDS接收器U28.经IC内部一系列处理后,输出的24位数字视频信号[PAB(7..O).PAG(7..O).PAR(7..O)]经保护电路后,直接送人Ull的数字视频输入端口PA(PAOO~PA23).供Ull内部的LCD图像处理器处理。与此同时,数据时钟信号DVICK,数据输出便能信号DVIDE.行、场DVI-HS/VS分别输至Ull(G4)、(F1)、(F2)、(G3)脚。

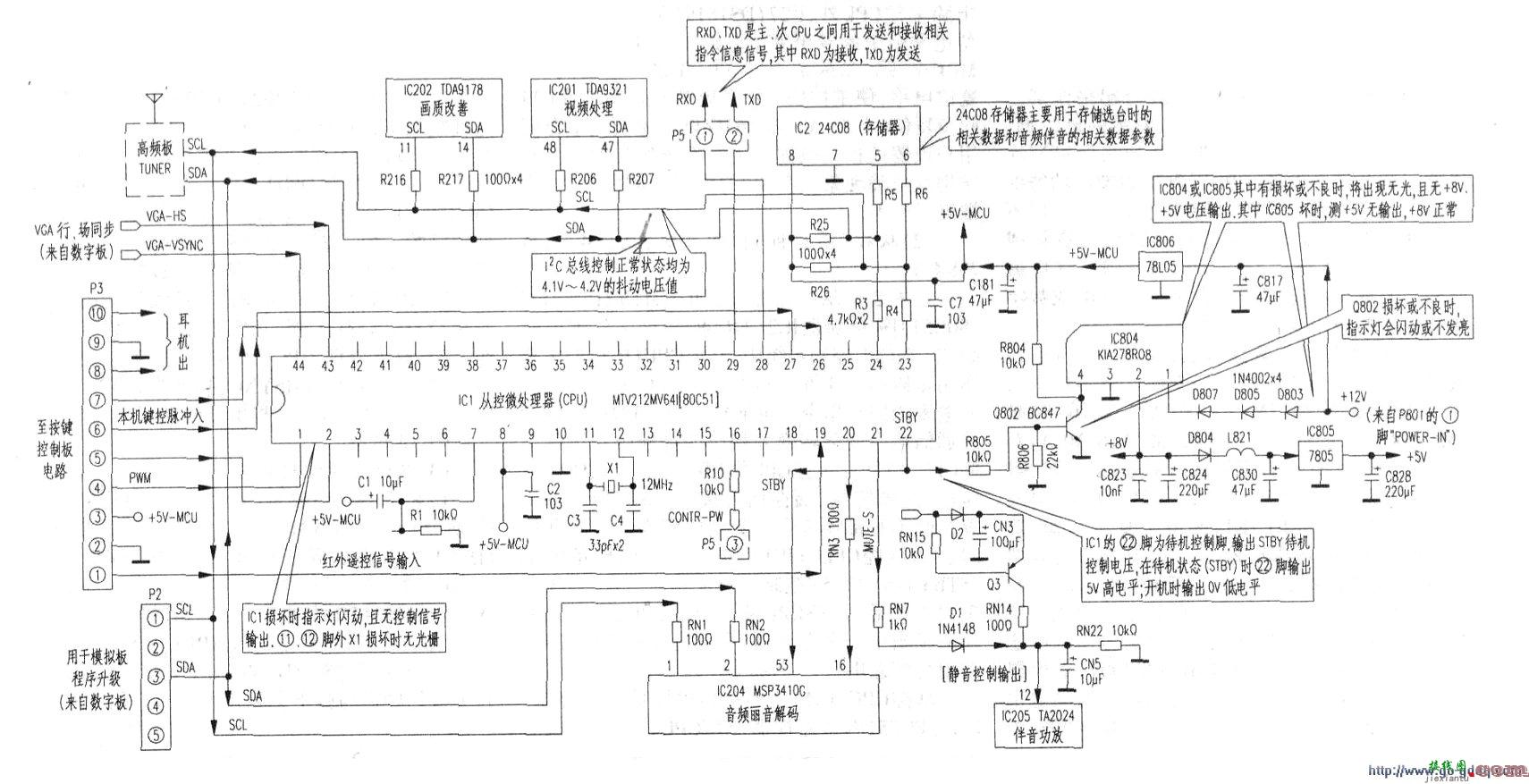

4.音频电路部分信号流程(见图下)

因平板电视电路结构普遍相对较复杂,为便于学习分析与理解,特将视频与音频信号流程部分分开介绍。

从下图可见,从高频头输出的第二伴音中频信号SIF,从高频板的接插件P3-2(7)脚输出,经耦合电容CN28输入至IC204(MSP3410G)音频丽音解码集成电路(50)脚(ANA-1+)。IC204是一块多标准丽音解码电路,它可对各种不同制式的数字伴音标准进行解码处理。IC204可根据当前的伴音格式是立体还是单声道伴音而选择高频头的SIF或AUDIO为输入。从AY1输入端口输入的一路音频信号经IC204(44)、(45)脚输入。

从AV2输入端口输入的一路音频信号经C19、C20、R33、R34及CN1、CN2耦合进入IC204的(42)、(41)脚。于是IC204根据当前的工作模式选择相应的输入通道信号,经lC内部的模,数转换电路转换、预换算或预处理电路处理、音频选择电路选择、再通过相应的音频处理电路处理后,作为耳机伴音的音频信号分别从IC204(17)脚(DACA-R)和(18)脚(DACA-L)输出右、左声道音频信号。该信号分别经RN5、CN35和RN6、CN36送到耳机伴音功率放大电路IC3(TDA2822D)(6)、(7)脚,经IC3音频功率放大后由(1)、(3)脚输出耳机音频信号。该信号主要用于监听或驱动小功率耳机发音。另一路音频信导分别从IC204(20)脚(DACM-R)和(21)脚(DACM-L)输出,输至IC205'TA2024)进行功率放大,经提升后的音频信号分别从IC205(24)、(27)、(28).(31)脚输出,经接插件SPI(1)、(2)脚和SP2(1)、(2)脚接至扬声器,推动主扬声器发声。

5.控制系统的控制机理与信号流程

整机控制系统由主CPUU19(80C32PLCC)和从控CPUICl(80C51)为主体组成主、从式控制系统。其中主控微处理器U19及其相关控制组件在数字板:从控微处理器ICI及其桐关控制组件在模拟板。故也可将其整机控制系统统称为数/模控制系统。就整体控制系统总体而言,相对较复杂些,为便于学习和掌握维修技能,下面用既分开又结合的方法加以解析。

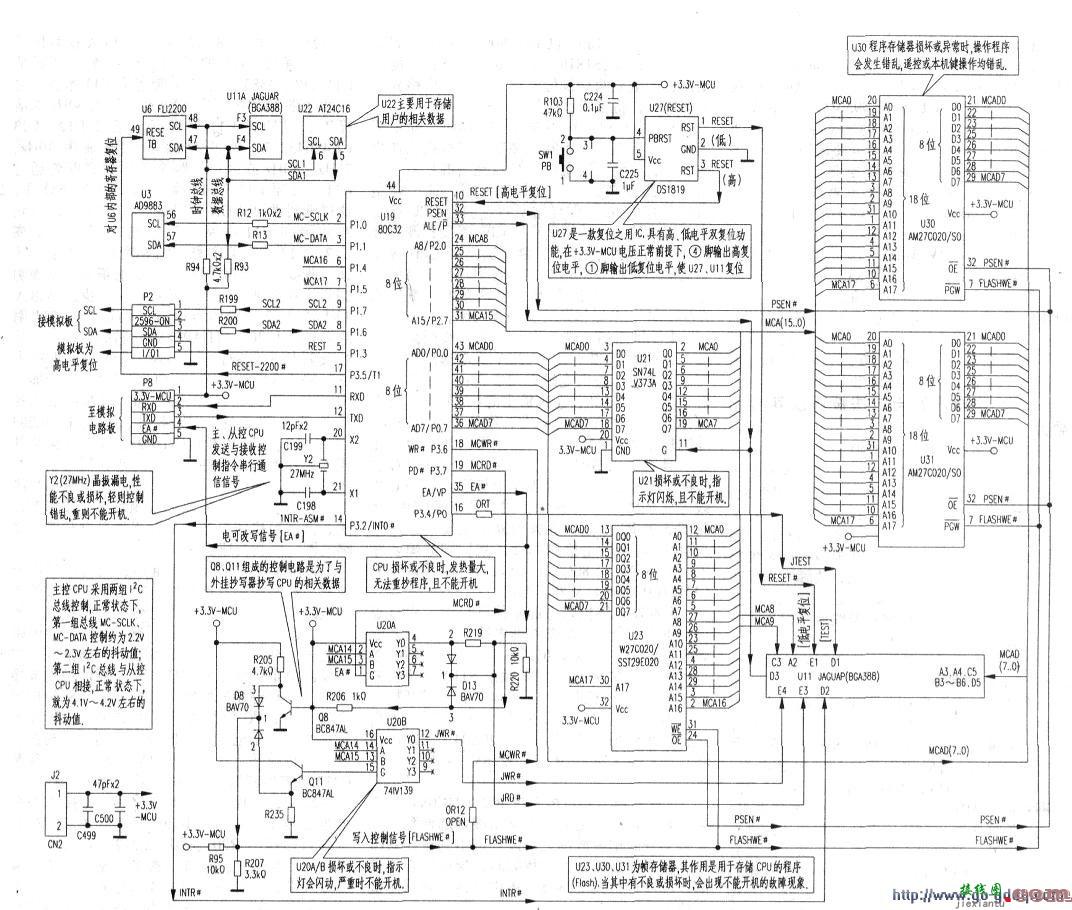

(1)主控(数字板)控制系统(见下图)

主要由主控微处理器U19(P80C32)、U20(74JV139)、U21(SN74LV373A)、U22(AT24C16)、U23(W27C02/SST2,9E020和U30、U31(AM27C020SOX2)等相关存储器组成。其主要任务和功能是:通过P2、P8连接插件的SCL、SDA总线;RXD、TXD((11)、(12)脚)接口向从控CPU(ICl)读取状态数据和发送控制指令,用自定义的串行通信协议实现通信。其中RXD为读取或接收;TXD为发送或发射接口。井通过SCL、SDA实现运作中的总线数据调整。主控CPU及其控制系统在正常运作过程中,除由源控制、遥控接收、键控指令译码、搜台控制、视频解码、丽音解调及TV/AV切换功能外,其余的操作控制及其处理,均由主控系统负责完成和进行运作。

主控系统的解读方法与技巧:乍看起来主控系统很复杂,其实根据笔者近三年来的学习解析与维修实践体会并非如此,只要掌握其相应的解读技巧便很容易解读,并实施有效的故障检修。经验与体会是:“层层归类拔取法。首先,将占用脚位较多的地址线(MCA)和地址与数据复用线(MCAD)所占用的脚位线看成一条连接线(因为引脚的作用和传输的信号都一样)。以下图的CPU(U19)为例,这样,就把大部分的脚位功能得以理解与拔除,这是第一步:第二步,再把供电脚、接地脚、空脚合起来作第二次拔除;第三步将平时常见且较熟悉的复位脚、晶振应用脚、IIC总线应用脚合并起来作第三次拔除。至此便会发现.CPU所剩下的脚位功能就所剩无几了,然后,便可对特殊功能脚或我们不易常见或较生疏的脚位功能通过相关资料或《英汉电子技术词汇》逐一研究和破解,这样就比较容易解读和理解新型数字平板彩电或数字集成电路的作用与引脚功能了。

下面,参照以上解读方法,来进一步解读该液晶彩电主控系统的机理与流程。主控CPU(24)-(30)脚(MCA8~MCA15)、(36)-(43)脚(MCADO~MCAD7)、(6)、(7)脚(MCA16、MCA17)均为地址线或地址,数据复用线引脚;第二步,(44)脚为供电脚,其余供电、接地、空脚未画出;第三步,(10)脚为复位端RESET(高电平复位),(20)、(21)脚为时钟振荡晶振脚,(2)、(3)、(8)、(9)脚分别为两组IIc总线控制端,其中(2)、(3)脚的IIC总线控制着数字板相关被控电路,(8)、(9)脚的IIC总线与模拟板相连接;(5)、(17)脚分别为复位信号控制电压输出端,分别控制数字板U6(FLI2200)、平板显示芯片和模拟板的复位,其复位状态为高电平复位。至此,剩下的引脚就极少了,其中(24)脚为自动搜索记忆或自动制式识别管理(INTR-ASM#):(16)脚为测试信号传输(TEST);接至Ull平板图像处理芯片JACUAP(BGA388)的Dl脚;(35)脚为电可改写控制信号(EA#),分别控制模拟板和数字板的Q8(BC847AL)b极,用于完成外挂抄写器抄写主CPU的相关工作数据;(19)脚为相位检测数字信号,接存储器U20A的(1)脚;(18)脚为写入控制信号端,分别连接相关存储器相应端。以上除主控CPU外.U27(DS1819)是一块高、低复位电平输出的专用复位电路RESET、在+3.3V-MCU电压正常的前提下.(3)、(1)脚各输出高、低复位电平,使主控CPU和平板图像处理芯片Ull同步复位。U22(AT24C16)存储器主要用于存储用户设置的相关数据。主控系统的其他功能和作用及故障现象已在下图的维修图解中标明,供维修时参考。

(2)从控(模拟板)控制系统(见下图)

它主要由从控微处理器ICl[MTV212MV641(80C51)]和存储器IC2(24C08)等相关外围电路组成。在CPU控制系统中,从控CPU(ICl)的主要作用是以串行中断方式接收主控CPU及其主控方送来的控制指令,再通过相应的I,o接口将相关通信信号变化转换为相应的遥控码回传给主控CPU,以便让主控CPU作相应处理。具体任务包括:电源控制、遥控信号接收、键控指令译码等,而不对接收信号作其他任何操作。刚开机时,由从控CPU(ICI)先启动输出预备电源(STBY)+8V和+5v控制信号及其他信号。当机器正常工作后,从控CPU是一个副cPu.此时它的功能相当于一个存储器,主要为主控CPU(U19)调用程序之用。

从控CPU(ICl)主要实施对模拟板的控制,IC1为80C51内核监视器专用CPU.内部集成有512Byte数据RAM、64kByte程序FLASH-ROM、AD转换器、IIC总线接口、自测图案发生器、行、场同步信号处理等功能。主要提供人机接口、模拟板设置及控制与数字板通信等。从下图不难看出,从控CPUICI的主要脚位功能有:(19)脚为红外遥控信号输入端,通过接插件P3(1)脚接至键控板电路。(11)、(12)脚为时钟振荡,外接Xl(12MHz)晶振及谐振电容。(15)脚为内部自测试图案视频输出。

(16)脚为对比度控制开关。(20)脚为复位控制,输出复位信号控制电压,控制音频丽音解码电路MSP3410G(IC204)的复位。(21)脚为静音控制端.控制伴音功放电路TA2024(IC205)(12)脚。(22)脚为待机控制端,输出STBY待机控制电压。在待机状态下(22)脚输出5V高电平;开机状态下输出ov低电平,从而控制Q802b极;同时控制IC204(MSP3410G)(53)脚。(23)、(24)脚为IIC总线时钟及数据控制端。(26)、(27)脚为面板按键控制信号输入端,通过P3接插件(6)、(7)脚与面板控制键相连接。(28)、(29)脚为主控CPU发送和接收相关指令信号端TXD和RXD.经插件P5(1)、(2)脚与数字板相连。(43)、(44)脚分别为PC机的VGA行、场同步信号输入端,其中(43)脚为HSYNC.(44)脚为VSYNC。其他从控CPU的维修资料与事项已在下图维修图解上标明,供参考。

(3)其他重点控制电路

1)背光(亮度)控制

U11(B1)脚输出的脉冲信号PWM1,控制着开关管Q3(DTC144EKA)的导通与截止,调整+5v电压对电容C172的充电.C172上的充放电所形成的线性电流经插件P7的(3)脚,从而实现控制背光的亮度。Ull的(AE22)脚输出的PENBKL背光源控制信号送至开关管Q5 (DTC144EKA)b极,通过控制开关管的导通与截止实现背光灯的开和关。

2)屏电源控制电路

Ull的(AD21)脚输出的PENYDD信号接到Q4 b极,并通过Q4 c极输出的信号来控制U14A (Si9953DY).U14A是一个MOSFET,C极接Q4的输出控制信号,S极接屏电压源(根据不同的屏要选用不同的供电电源),D极是屏电源的输出端。

3)复位信号的处理与控制电路

U27 (DS1819)是一个输出复位信号的专用集成电路,它可以同时输出高、低两种复位信号电压。当+3.3V-MCU电压正常时,(4)脚输入一个高电位,此时(1)脚为低电平复位电压输出;(3)脚为高电平复位电压输出,使主控CPU(U19)和平板图像处理芯片Ull同时复位。

注:(1)、(3)脚组成的高、低电平复位是为了配合不同集成电路复位而设置的,因为有的IC是高电平复位.有的则是低电平复位。

相关文章

发表评论