全面的电子元器件实物图+电路符号,值得收藏!-电子技术方案|电路图讲解

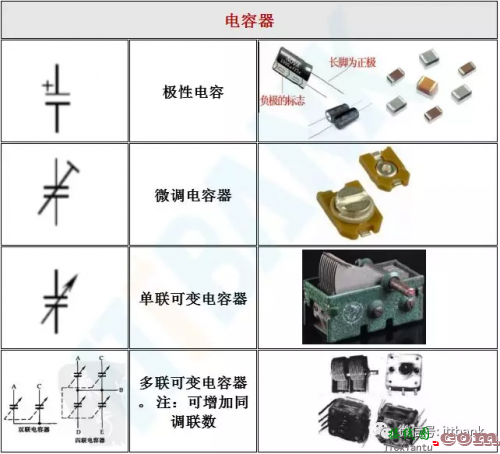

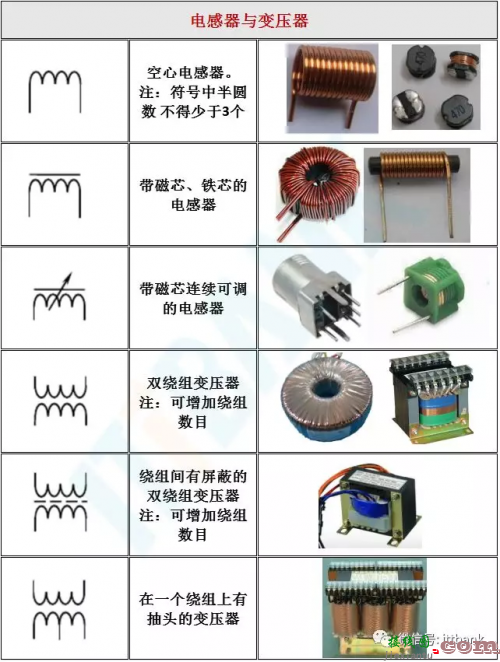

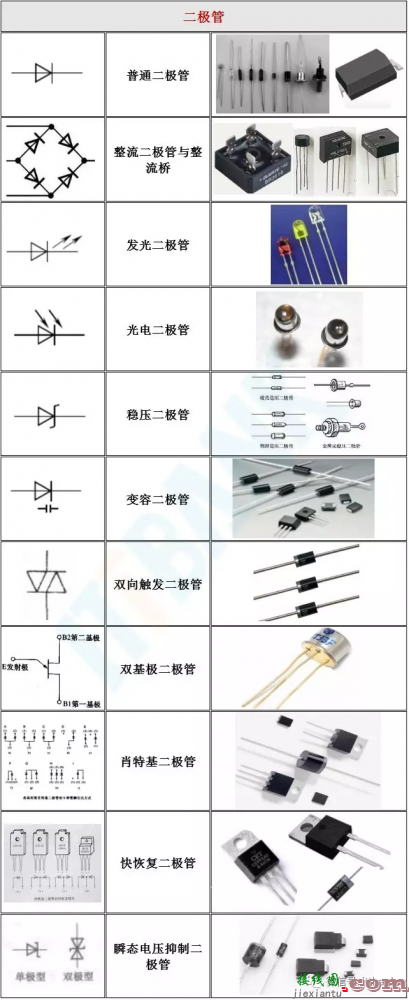

将许多电阻器、二极管和晶体管等电子元器件以电路的形式制作在半导体硅片上,然后接出引脚并封装起来,就构成了集成电路,又称芯片IC。所以这些基本的电子元器件起着至关重要的作用,下面一起来看看它们的实物外形图与电路符号:

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选项替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

验证(verification)是现代数字集成电路设计流程中不可或缺且至关重要的一环,其目的是保证设计功能按照既定的设计规约正确的实现。在一个完整的项目周期中,验证所占用的时间可高达60%-70%。按验证的具体目的,可以有很多种细分类别,而本文主要针对其中的“功能验证“,即只专注于设计逻辑功能的实现,而暂不考虑综合、布局布线后引入的电路延时与优化,从而导致的硬件与实际逻辑出现偏差的情况。

目前业界主流的验证方法主要是以UVM(Universal Verification Methodology)为代表的验证方法学,通常使用随机约束的方式,在电路仿真中自动产生受控的随机输入,从而驱动验证电路并完成验证功能。随着UVM的发展和广泛使用,特别是其中SystemVerilog语言加入了面向对象、功能覆盖、随机约束等更加类似软件开发的特性,使得验证平台间模块重用的效率得到提升,编程结构化变好,代码更加灵活。有关这些传统的验证方法的讨论和思考会在下文中逐步给出。

然而需要注意到的是,这些基于电路仿真的验证方法存在较多的根本性问题一直无法有效解决,如对极端情况的覆盖、过长的仿真时间、调试难度较大等等。这些问题也将会在后文一一讨论。在2018年初,几乎全部主流的CPU厂商都被发现在其CPU产品中存在熔断(Meltdown)和幽灵(Spectre)漏洞。这也在一个侧面表明,当代集成电路验证存在极高的复杂性,特别是对于大型设计而言。因此,业界一直在寻找其他更为有效的验证方法学。下文将介绍的“形式化验证“(Formal Verification)就是其中之一。

图1:熔断(Meltdown)和幽灵(Spectre)漏洞

什么是形式化验证

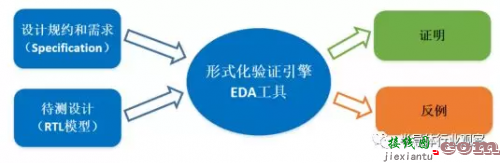

和基于电路仿真的验证方法不同,笔者认为形式化验证的定义是:利用形式化方法,即基于严格的数学表述和模型,根据设计规约对设计功能进行属性描述,并自动进行数学分析和证明。这看上去似乎非常玄妙,但实际上形式化验证的过程可以粗略的由下图描述:

图2:形式化验证简要流程图

它很像我们上学时做过的数学证明题,即给一个命题,用数学定理和方法证明该命题是否成立。若不成立则给出一则反例。在形式化验证中,待测设计的某个功能和设计规约对应的描述就是命题的两部分,命题为证明二者是否等价,若得证则表示在任意情况下命题成立,若不得证则表示命题不成立,且会给出一个反例。这个推理和证明的过程通常由EDA工具自动完成。目前,业界主流的形式化验证EDA工具主要有Cadence的JasperGold,和Synposys的VC-Formal等。

需要注意的是,作为形式化验证的使用者,我们并不需要了解形式化方法的具体数学原理,亦或是证明的具体过程。在多数情况下,在形式化验证工具里的调试过程和传统电路仿真工具十分类似。在下一章,我将详细介绍形式化验证相比传统验证方法的主要优势。

形式化验证的主要优点

与传统的基于仿真的验证方法相比,形式化验证主要有以下三个方面的优点。

第一,形式化验证能覆盖完整的设计状态空间。

与其他所有基于仿真的验证方法相比,这一点是形式化方法最大的优势所在。通常来讲,一个数字电路的设计通常由若干个逻辑状态空间(logic state space)组成,这其中可以包含以下几类状态:

电路复位后的初始化状态, 也称为复位状态;

内部逻辑实现时的中间状态;

各个输入输出的状态。

比如,在一个FIFO设计中,它的“满”、“空”指示就是输出的状态;在某一时刻,FIFO里内存的读写指针的位置就是中间状态;而当复位完成后,指针位置以及当时“满”、“空”指示的值就是复位状态。

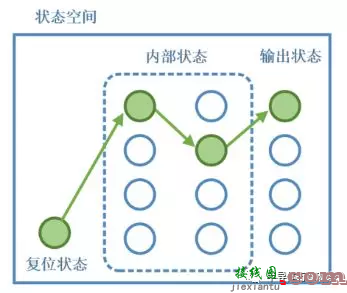

如果将这些状态抽象提取出来,我们可以得到针对这个设计的完整的状态空间,如下图所示,其中每一个圆圈都代表电路中的一个可能的逻辑状态。而验证的最终目的,就是对完整的状态空间进行覆盖,并确定其满足既定的设计要求。

在电路仿真中,每次仿真实际上就是在状态空间里寻找一条从“复位状态”到“输出状态”的路径, 如下图中标出的一条路径。

图3:一次仿真得到的状态路径

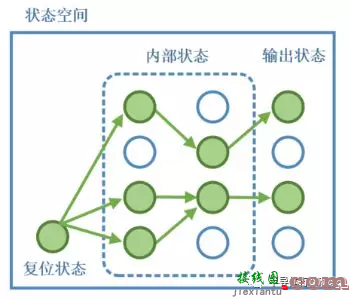

需要注意的是,在仿真中每条路径的确定与仿真使用的输入(也称为激励或测试向量)有着密切的关系。如果在每次仿真中使用不同的输入,例如采用随机约束的验证方法,那么有可能找到更多的状态路径,如下图所示。

图4:多次仿真得到的状态路径

然而,对于某些大型设计,即便使用了多种不同的输入,也有可能仍然找到相同或者部分重叠的路径,这样就导致某些状态很难被覆盖,即我们通常所说的“边界情况”(corner cases)。对于边界情况的处理,通常的做法是增加仿真次数,即尝试更多不同的输入组合;延长仿真时间;或者针对其创建新的“定向测试”等。然而不管使用何种方法,都会极大的增加完成验证所需的时间,以及投入的各类成本。最根本的问题在于,即便使用了这些方法,也并不能保证边界情况被100%覆盖,这是由于仿真无法遍历所有可能的输入向量。换句话说,基于仿真的验证只是检验了在使用某些测试向量时,系统不会出现漏洞,但无法保证当使用其他测试向量时,漏洞不会出现。上文提到的CPU “熔断”和“幽灵”漏洞,也从另一个角度很好的印证了这一点:一方面,我相信英特尔(及其他厂商)在设计芯片时已经进行了充分验证,但显然还存在边界情况。另一方面,即使芯片已上市并广泛使用多年,这些漏洞直到最近才被发现,这在一定程度上表明通过改变测试向量来进行边界情况的捕捉和覆盖,效果不够理想,往往更像是“大海捞针”。

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选项替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

相关文章

发表评论