如何解决电气中的谐波问题?-原理图|技术方案

摘要:由于电力电子技术的飞速发展,各种电力电子装置在电力系统、工业、交通及家庭中的应用日益广泛,谐波所造成的危害也日趋严重,如何治理电气中的谐波问题,已经成为世界各国的重中之重。

背景一:2003年8月17日,美国纽约大停电,数万居民在一年中最热的天气下“煎熬”了5天,发生60起重大火灾,一天经济损失200-300亿美元。

背景二:九十年代初,三列电气机车同时在山西石洞口电厂供电区域通过,结果将经过十几次锻打的12.5兆瓦发电机组主轴扭成“麻花”,西北电网因此解网,发生电力系统最高等级恶性事故。

背景三:某大型钢铁公司70吨交流电弧炉,由于没有安装电力滤波装置,一台9万千伏安变压器瞬间被烧坏,损失500多万元。

触目惊心的事故,发人深思的教训。这一切都指向同一个源头:谐波。谐波的危害十分严重,谐波使电能的产生、传输和利用的效率降低,使电气设备过热、产生振动和噪声,并使绝缘老化,使用寿命缩短,甚至发生故障或烧毁,最终造成巨大损失。

谐波,对电力系统环境的影响和危害不能小觑。由于谐波污染范围大、距离远、传播快,对电网的污染比之于一个问题化工厂对大气环境的污染更为严重。据权威测算,仅江苏一个省,每天因谐波而浪费的电就有上亿度。

如何治理电气中的谐波?

既然谐波存在多方面的危害,采取必要的有效手段,避免或补偿已产生的谐波,就显得尤为重要。谐波的治理可归纳为以下治理措施:

(1)加强标准和相应规范的宣传贯彻。IEC 61000以及国标GB/T 14549-1993,对于谐波定义、测量等进行了宣传,明确谐波治理是一项互惠互利、节能增效,是保证电网和设备安全稳定运行的举措;

(2)主管部门对所辖电网进行系统分析,正确测量,以确定谐波源位置和产生的原因,为谐波治理准备充分的原始材料;在谐波产生起伏较大的地方,可设置长期观察点,收集可靠的数据。对电力用户而言,可以监督供电部门提供的电力是否满足要求;对于供电部门而言,可以评估电力用户的用电设备是否产生了超标的谐波污染;

(3)针对谐波的产生和传播的特点,采取相应的隔离、补偿和减小措施。在配电网中,主要存在的是三次谐波污染,可以在谐波检测的基础上,通过适当加装滤波设备来减小谐波注入电网。对于各种电气设备的设计者,在设计初始,就要考虑其设备的谐波污染度,将谐波限制在标准允许的范围内。

电压毛刺脉冲在信号链路径中很常见,特别在系统加电或断电时更是如此。根据峰值幅度和毛刺脉冲持续时间的不同,系统输出中的最终结果会是灾难性的。其中的一个示例就是工业电机控制系统,在这个系统中,数模转换器 (DAC) 驱动电机驱动器,以控制电机旋转。如果毛刺脉冲幅度高于电机驱动器的灵敏度阈值,当系统加电/断电时,电机会在没有任何方向控制的情况下旋转。

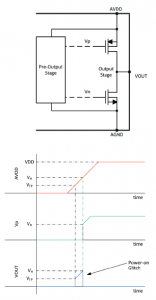

图1.经简化的输出级和加电毛刺脉冲

之前已经分析了高精度DAC经缓冲输出出现加电/断电毛刺脉冲的原因和减少这些毛刺脉冲的解决方案。这份简报主要介绍了DAC输出缓冲器在加电至电压输出模式时出现的加电毛刺脉冲。一个高精度DAC可以在多个配置中加电:零量程、中量程,或是高阻抗。用户可以控制预断电状态。某些DAC具有内置的加电毛刺脉冲减少 (POGR) 电路;这个电路在DAC输出级未被驱动的配置中保持DAC的输出级。经缓冲电压输出DAC具有一对作为输出级的PFET和NFET。POGR电路禁用PFET,并将NFET偏置到其阈值电压 (VTH) 以上,从而最大限度地将加电毛刺脉冲减少到几百毫伏。

并不是每个DAC中都有POGR电路。对于没有POGR的DAC来说,加电/断电毛刺脉冲取决于多个因素:

1.DAC到电压输出模式和高阻抗模式的加电状态

2.DVDD、VREF、IOVDD和其它电源引脚的加电顺序

3.反馈网络连接

4.电源斜升速率

5.输出阻性负载

这篇文章所讨论的是输出级被加电至电压输出模式的情况。在这个模式下,PFET和NFET的栅极由一个预输出级控制。这个预输出级需要一个特定的最小电压来正常启动。这个电压也被称为最小净空 (VH)。这个电压取决于预输出级架构,并且可高至6V。这个电压远远低于数据表中所规定的最小电源电压 (VDDMIN)。通常情况下,大多数数据表中并未指定此电压。

在达到这个最小净空电压前,预输出级没有足够的净空来实现正常运行。因此,输出FET栅极可以低至0V,这使得PFET可以在电源电压与PFET阈值电压 (VTP) 相交时,运行为电源与输出引脚之间的低阻性开关。因此,输出能够随着电源斜升,从而导致了加电毛刺脉冲(请见图1)。

在这个情况下,毛刺脉冲电压可以高达最小净空电压 (VH)。由于预输出级的净空不足,所以这个毛刺脉冲与电源斜升速率无关。所有DAC数据表都规定了一个输出上的最小阻性负载(通常为1kW)。将一个阻性负载加载到DAC输出上是尽可能减小这个毛刺脉冲的常见技术。然而,这项技术并不能最大限度地减少毛刺脉冲幅度,这是因为输出PFET运行为一个电源与输出引脚之间的开关(或短接)。加电序列和反馈网络连接会进一步加大这个毛刺脉冲。由于这些因素通常是相互关联的,它们都作为一种情况进行分析。

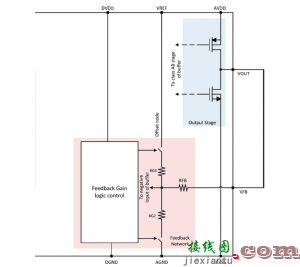

图2.具有反馈网络的输出级。

对于具有双极输出的双电源DAC来说,反馈网络还包括一个偏移节点。这个节点可由基准引脚上的固定电压 (VREF) 驱动,或者由一个偏移DAC驱动。偏移DAC在用户需要小电压偏移输出时有用,从而实现一个不对称的输出范围;例如,从-5V至+10V。

图2是一个具有反馈网络的输出级的简化图。这个反馈网络需要开关来改变DAC的增益和偏移。这些开关有一个单独的数字电源,或DVDD供电。根据DVDD加电序列的不同,增益/偏移路径会为开路,或者短接至VREF/AGND引脚。这会在启动期间导致一个错误增益设置,并且会形成加电毛刺脉冲。在大多数多电源DAC中,建议使用一个特定的加电序列来避免这一情况的发生。

加电毛刺脉冲与DAC寄存器的状态无关。在DAC有一个被称为加电复位 (POR) 的电路供电时,所有DAC寄存器均保持在复位状态。当一段时间后,这些寄存器从复位状态中被释放出来时,输出和预输出级就具有足够的净空来正常运转了。

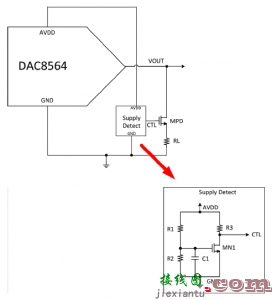

图3.简单电源检测电路

一个简单电源检测电路(图3)可被用来在电源斜升期间立即载入DAC输出。DAC输出VOUT在电源斜升期间,通过FET MPD,用电阻器RL载入。这个电源检测块生成MPD控制。在电源斜升期间,控制信号CTL被拉至AVDD,在FET MN1被接通前,用负载RL载入DAC输出VOUT。在MN1被完全接通后,它将CTL节点拉至接地,卸载VOUT节点。必须根据MN1的阈值电压来设定R1、R2、R3和CL的大小。

这篇文章分析了加电毛刺脉冲和它形成的根本原因。虽然其中的分析主要是用来解决加电毛刺脉冲,不过同样的原理也适用于断电毛刺脉冲。特定DAC在没有内部POGR电路的情况下,在正常模式下被加电,在启动期间,输出引脚与接地之间的一个小的阻性负载是尽可能减少这些DAC加电毛刺脉冲的唯一方法。

-电子元器件采购网(www、oneyac、com)是本土元器件目录分销商,采用“小批量、现货、样品”销售模式,致力于满足客户多型号、高质量、快速交付的采购需求。自建高效智能仓储,拥有自营库存超50,000种,提供一站式正品现货采购、个性化解决方案、选型替代等多元化服务。 (本文来源网络整理,目的是传播有用的信息和知识,如有侵权,可联系管理员删除)

相关文章

发表评论