单晶收发器系统采用10.240MHz基准频率,添加到VC0频率,产生发射频率。同样的10.240MHz基准频率混合个中频信号,产生455kHz第二中频...

多协议完全集成13.56MHz近场通信收发器集成电路设计

TRF7970A是一款高性能13.56MHz高频RFID/NFC收发器IC,此器件由一个集成的模拟前端和一个针对ISO15693,ISO14443A,ISO14443B,和FeliCa的内置数据组帧引擎组成。这包括针对ISO14443的高达848kbps的数据速率,包括板上全部组帧和同步任务(在默认模式下)。TRF7970A也支持NFC标签类型1,2,3,和4操作。这个架构使得用户能够建立一个完整且划算而又高性能的多协议13.56MHzRFID/NFC/NFC系统和一个低成本微控制器。通过使用器件提供的直接模式中的两个,可执行其它标准,甚至定制的协议。这些直接模式(0和1)使得用户能够完全控制模拟前端(AFE)并获得到原始副载波数据或者非成帧数据(但已经是ISO格式数据)和相关(被提取的)时钟信号的存取权限。

接收器系统有一个双输入接收器架构。此接收器还包括多种自动和手动增益控制选项。接收到的输入带宽可被选择来包含广泛范围的输入副载波信号选项。通过RSSI寄存器可获得接收到的来自应答机、周围信号源或者内部电平的信号强度。接收器输出可在一个数字化副载波信号和任一集成型副载波解码器间进行选择。所选择的副载波解码器将数据比特流和数据时钟作为输出发送。TRF7970A还包括一个接收器组帧引擎。这个接收器组帧引擎执行CRC或者奇偶校验,移除EOF和SOF设置,并且将数据组织成用于ISO14443-A/B,ISO15693,和FeliCa协议的字节格式。然后通过一个128字节FIFO寄存器,微控制器(MCU)可访问已组帧的数据。

TRF7970A使用并行微控制器接口的读取器系统

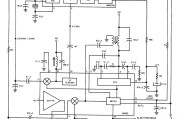

图4显示了最灵活的TRF7970A应用电路原理图。ISO15693,ISO14443和FeliCa系统都可被设定地址。由于DATA_CLK线路上的低时钟频率,并行接口是将TRF7970A连接至MCU的最稳健耐用的方法。匹配至一个50Ω端口,这样可实现到一个适当匹配的50Ω天线电路或者RF测量设备的连接(例如,一个频谱分析仪或者一个功率计)。

图显示了一个并行MCU接口的示例应用电路原理图

一个MSP430F2370(32kB闪存,2kBRAM)显示在图4-1中。最小MCU需求取决于应用要求和编码风格。如果只需支持一个ISO协议或者一个协议的有限命令集,则对于MCU闪存和RAM的要求将会大大减少。请注意递归目录和防冲突命令比单槽运行要求更多的RAM。例如,ISO15693(含主机接口)目前的基准固件大约为8kB,使用512BRAM;对于所有支持的协议(具有同样的主机接口),此基准固件接近12kB并且最少使用1kB的RAM。为了实现直接模式0运行需要一个GPIO运行频率能达到13.56MHz的MCU。

TRF7970A使用包含从器件选择(SS)模式的SPI读取器系统

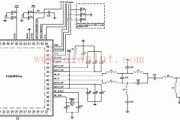

图显示了针对使用串行端口接口(SPI)的ISO15693和ISO14443系统而进行了优化的TRF7970A应用电路原理图。较短的SPI线路,无线电设备频率线路的正确隔离,和一个恰当的接地区域对于避免干扰十分重要。DATA_CLK线路上的推荐时钟频率为2MHz。匹配至一个50Ω端口,这样可实现到一个适当匹配的50Ω天线电路或者RF测量设备的连接(例如,一个频谱分析仪或者一个功率计)。电路原理图显示了一个具有SS模式MCU接口的SPI的示例应用电路原理图。

一个MSP430F2370(32kB闪存,2kBRAM)图。最小MCU需求取决于应用要求和编码风格。如果只需支持一个ISO协议或者一个协议的有限命令集,则对于MCU闪存和RAM的要求将会大大减少。用户应该注意递归目录/防冲突命令比单槽运行要求更多的RAM。例如,ISO15693(含主机接口)目前的基准固件大约为8kB,使用512BRAM;对于所有支持的协议(具有同样的主机接口),此基准固件接近12kB并最少使用1kB的RAM。为了实现直接模式0运行需要一个GPIO运行频率能达到13.56MHz的MCU。

相关文章

发表评论