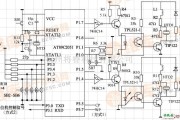

图1所示是由六反相器74HC14、功率管TIP 122以及单片机AT89C2051等组成的电机多操作...

2024-04-15 211 数字电路

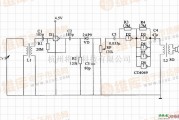

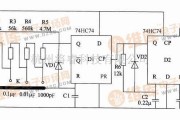

是一个采用数字集成电路的延迟灯,图中只卅到CD4069中三只完好的

反相器,另三只反相器牢着不用并将它们的输入端接地以消除对电路的干扰。

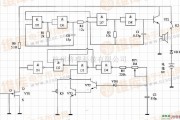

甲时,反相器J的输

入端①脚川电阻R.而处于

高电平,反柑后输出低电

平,二极管vr)i截止,反

相器Ⅱ输入端③脚为低}U

平,这时“充满rl.lF F

负的电荷。③脚的低电平

经反相器II、爪曲级反牛H

后输出仍为低电平,所以

此时三极管VT截止,继

电器K不动作,其触点k-l打开,电灯E不亮。如果按一下开关SB,反柏器l的

输入端①脚变为低电乎,反相后输出高电平,VD1导通,使反相器Ⅱ的输入端③

脚也变为l断电平,这时c,经VD1放电。此高电平经两级反相后,使⑥脚为高电

平,经亿加到VT的基极使VT导通,继电器K得电吸合,其动合触点k1闭台,

电灯F通电发光。松开SB后,虽然反相器T的输入和输出端电平发生翻转,VDl

截lF,但山于('_两端电压小能突变,③脚和⑥脚仍保持高电平小变,所以继电器

K仍维持吸合态。此时电源经R.向C克电,使③脚电平逐渐下降,当电平降至

l/2Vm(即CMOS电路司值电/)叫,反相器Ⅱ、Ⅲ输入和输出电平均发生翻转,

⑥脚由原来的高电平变为低电甲,VT即截止,继电器K失电释放,触点复位,电

灯E熄火。本电路延迟时问主要由R,和G的克电时问常数决定。

由丁数宁集成电路具有高输入阻抗,C.要求采用漏电流极小的电解电容嚣,

如有条件,蛀好采用钽电解。c.要求使用CBn-400V型等聚丙烯电容器,K用

JZC-22F、DC12V小型中功率电磁继电器。

相关文章

图1所示是由六反相器74HC14、功率管TIP 122以及单片机AT89C2051等组成的电机多操作...

2024-04-15 211 数字电路

由一片6反相器CD4069组成的信号接受电路 如图是由一片六反相器CD4069组成的信号接收电路图,该电路可接受较强的广播信号,其接受频率为53...

2024-04-15 264 数字电路

电子报警电路 如图所示是由四2输入端与非门CD4011、场效应管和晶体三极管等构成的电子报警电路。当报警电路被触动时,就会发出报警信号。 在图...

2024-04-15 264 数字电路

如图所示电路由四2输入端或非门74HC02、串接二极管4148 X 2、数码显示管等组成。该电路主要...

2024-04-15 211 数字电路

如图所示是由双上升沿D触发器74HC74组成的电容容量测量电路。该电路外接万用表时可将测量出的结果显示出来。 电容容量测试量电路 在电路图中...

2024-04-15 316 数字电路

如图所示电路是由4位二进制同步加/减计数器74HC193、双上升沿D触发器74HC74以及四2输入端与非门74HC00等组成的光电编码器鉴相计数电...

2024-04-15 226 数字电路

发表评论