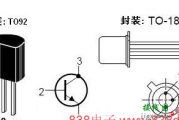

2N2222/2N2222A 是一小功率NPN三极管,封装形式有TO-18,TO92两种封装如下图所示。可与2N2907/2N2907A PNP管做互...

放大倍数为40的放大电路设计

接线图

2023年07月14日 22:19 287

admin

打算设计一个放大倍数为40的放大电路,采用三极管分立元件或集成运放皆可实现,但对于初学者来说,采用集成运放设计更简单。

以下是一款采用集成运放设计的40倍放大电路,不仅可以用于放大交流信号,也可以用于精确放大直流信号,且工作状态十分稳定。

图1:集成运放设计的40倍放大电路

A为集成运放,这里接成同相放大器,电阻R1为反馈电阻。电路的放大倍数为1+(R1/R2),当R1=39千欧,R2=1千欧时,电路的放大倍数即为40。

本电路的输入电阻等于R3的阻值。C1和C2为耦合电容。电路的工作电压范围与集成运放的型号有关。

为了减小温度对放大倍数的影响,电路中的R1、R2应选用温度稳定性好的金属膜电阻,且两个电阻的误差≤1%。

由于运放A的开环放大倍数很大,工作于负反馈状态时,其闭环放大倍数只与外接的电阻R1、R2有关,而与运放无关。即使更换不同型号的集成运放,本电路的闭环放大倍数也不会发生变化,这个放大电路交直流信号皆可放大。

如果用于放大交流音频信号时,可以选用输入噪声小、失真小、转换速率高的音频运放,比如:NE5534、LM833等。如果用于放大缓慢变化的超低频信号或直流信号时,则可以将耦合电容C1和C2省略,A选用ICL7650或OPA177等超低失调电压运放。

相关文章

发表评论