电容三点式振荡器 电容三点式振荡器是一种电子元件,也叫考毕兹振荡器,是自激振荡器的一种。由串联电容与电感回路及正反馈放大器组成,因振...

HD14538构成的定时电路图原理讲解

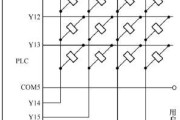

接线图

2023年07月21日 22:41 313

admin

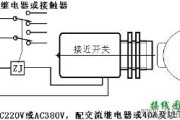

在启动前 Q (⑥脚) 输出为低电平, T2 (②脚) 端外接电容上电压为 U DD 。 当 A (④脚) 为0, CD (③脚) 为1 时, 若 B(⑤脚) 从 1→0 负沿触发, 则输出锁存置位, Q 输出高电平。

触发工作时, 若在 Q 输出为低电平之前加触发, 则为预触发, 从最后触发到定时工作 Q 输出为低电平。 若 CD 输入 0, 则T2 的外接电容充电, 充电到 U ref2 , 输出锁存复位, 电路恢复初始状态。 CD 为 0 状态时, 若再输入脉冲, 电路不动作, 输出为低电平。

Q (⑥脚) 输出高电平, VT1 导通, 使继电器 K 动作, 其触点控制相关电路工作。 电路中, R1、 C1 和 C2 构成滤波电路,防止噪声干扰使电路误动作。 不用输入脚接地, 即⑭ ⑪、 ⑭ ⑫和⑭ ■脚接地。 HD14538 构成的定时电路如图所示。

图 HD14538 构成的定时电路

相关文章

发表评论