PIN光电二极管是在PN结的P型层和N型层之间夹了一层本征半导体(semiconductor ,形成P-I-N结构而得名,如下图所示:如上图所示,处于...

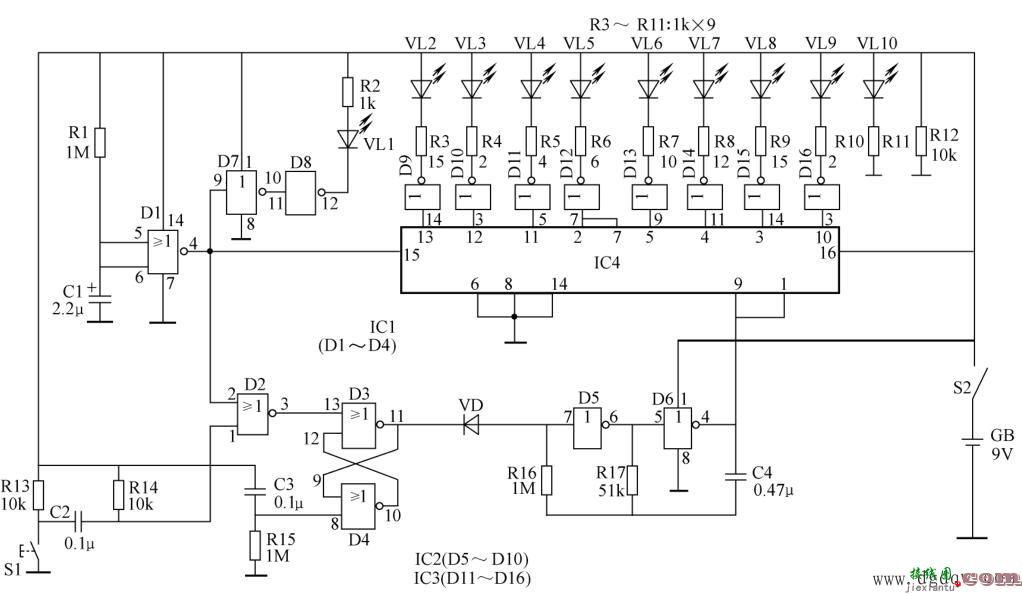

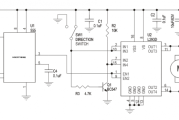

反应能力测试电路图原理

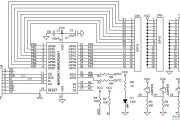

接线图

2023年07月21日 22:41 319

admin

图 反应能力测试电路

接通电源开关 S2 后, 电源指示发光二极管 VL10 点亮。 在开机瞬间, 由于 C1 两端电压不能突变, D1 的输入端为低电平,输出端为高电平。 此时 D7 输出低电平, D8 输出高电平, LED1不发光; 多谐振荡器振荡工作, 为 IC4 提供周期约为 50ms 的时钟脉冲。 IC4 在该时钟脉冲的作用下, 各输出端依次逐端变为高电平。 通过 D9 ~ D16 反相缓冲后使 LED2 ~ LED9 依次递增发光,直至全部点亮。

当 C1 充满电 (约 3 ~4s) 时, D1 的输出端变为低电平, 使D7 输出高电平, D8 输出低电平, LED1 点亮。 同时, IC4 因⑭ ⑮脚输入低电平而由加法计数变为减法计数, 在时钟脉冲的作用下, 其各输出端从左至右依次逐端变为低电平, 使 LED2 ~ LED9依次递减熄灭。

在 VL1 点亮的同时, 若测试者在 50ms 之内按下 S1, 则 D3的输出端变为低电平, VD 导通, 迫使多谐振荡器停振, IC4 保持加法计数、 VL2 ~ VL9 全部点亮的状态; 若测试者在大于50ms、 低于 100ms 的时间内按下 S1, 则 IC4 已进入减法计数状态, 其⑭ ■脚 (1Q1 端) 已变为低电平, 使 VL2 熄灭, 但 VL3 ~VL9 仍维持点亮状态; 若测试者在大于 100ms、 低于 150ms 的时间内按下 S1, 则 IC4 的⑭ ⑫脚 (1Q2 端) 也变为低电平, 此时VL2 和 VL3 熄灭, VL4 ~VL9 仍点亮。 以此类推, 若测试者在 VL1点亮 400ms 之后才按动 S1, 则 VL2 ~ VL9 已全部递减熄灭。 即按下 S1 后, 点亮的发光二极管数量越多, 说明测试者的反应速度越快; 点亮的发光二极管的数量越少, 说明测试者的反应速度越慢。

相关文章

发表评论