电容三点式振荡器 电容三点式振荡器是一种电子元件,也叫考毕兹振荡器,是自激振荡器的一种。由串联电容与电感回路及正反馈放大器组成,因振...

单片机晶振电路的原理和作用图解

接线图

2023年07月21日 22:42 267

admin

在单片机的学习中,不光是单片机程序的编写,还有电路的设计。有些公司可能会把单片机开发分成两块:电路设计、程序设计。然后负责电路设计的人只负责电路设计,不用考虑单片机编程;程序设计的人只管单片机编程,不设计电路。

不过我个人认为,只搞电路设计的人可以不用关心单片机是怎么编程的,但是搞单片机程序设计的人,却必须要对电路很熟悉,你可以不用亲自设计电路,但是必须对单片机项目中各种电路的原理足够了解,这样才能确保设计出来的程序稳定、健壮。

举个例子来说吧,假如一个单片机系统中用到了EEPROM存储芯片,EEPROM芯片的SCL和SDA是开漏输出的,需要外接上拉电阻,假设电路板上的EEPROM芯片的SCL和SDA的上拉电阻忘记焊上或者坏掉了,这时候调试EEPROM是调不通的,如果这时候电路设计人员不在,而单片机程序设计人员又对EEPROM的原理不熟悉,就会陷入到麻烦中:因为对电路不熟悉,就会一遍一遍的查找程序的原因。可是程序明明没有问题啊,这个程序在别的项目中一直都是正常的,为什么在这个板子上就不行了呢?

综上所述,单片机程序设计人员一定要对电路的原理熟悉,这样才能设计出正确的程序。

从本篇文章开始,我们就来简单学习一下单片机开发中常用的电路。

当然,由于本人水平有限,关于这些电路的讲解只限于简单原理的讲解。如果有错误,欢迎批评指正。

1. 单片机常用电路1-晶振电路

早期的单片机(比如经典的51单片机)系统,外接晶振是必须的(当然也可以外接时钟脉冲,但是很少用),因为单片机的运行必须依赖于稳定的时钟脉冲。但是随着技术的发展,现在很多单片机都已经集成了内部时钟,所以在一般的应用场合,可以不用外接晶振电路了。不过由于内部时钟容易受外界干扰,所以在要求严格的场合,晶振电路还是很有必要的。

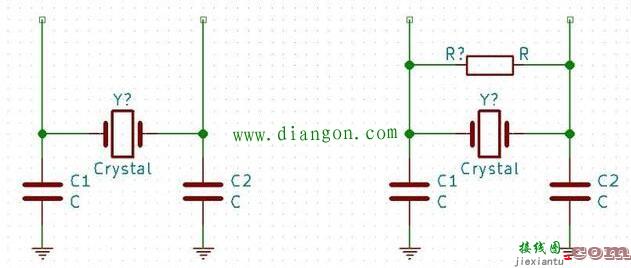

图1是典型的单片机外接晶振电路。

图1 单片机晶振电路

该电路不只是有一个晶振,还有两个电容,这两个电容有什么作用呢?

这两个电容一般称为“匹配电容”或者“负载电容”、“谐振电容”。晶振电路中加这两个电容是为了满足谐振条件。一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。只有连接合适的电容才能满足晶振的起振要求,晶振才能正常工作。

负载电容的值由如下公式计算:

负载电容无法满足的话一般会使晶体频率产生偏差,严重的话晶体无法起振。电路设计中要尽量满足晶体的负载电容需求,从而使晶体工作在最佳状态。负载电容计算公式如下:

CL = C1*C2 / (C1+C2) + CS

CL为晶振的负载电容值,一般通过查询晶振的数据手册获得。CS为电路板的寄生电容,一般取 3~5pF,取C1 = C2,那么公式可以简化成如下:

CL = C1 / 2 + CS

一般情况下,增大负载电容的值会使振荡频率下降,减小负载电容的值,会使振荡频率上升。

晶振电路2

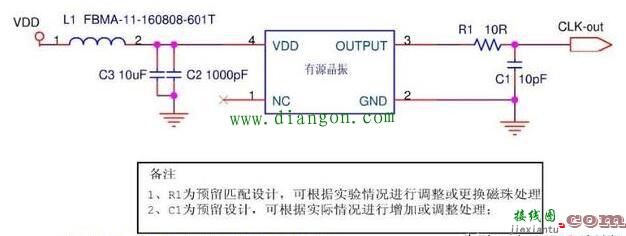

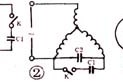

我们有时候还会看到如图2所示的晶振电路。

图2 不带并联电阻和带并联电阻的晶振电路

该电路中晶振上又并了一个电阻,这是为什么呢?

这个电阻实际上是反馈电阻,是为了方便晶振起振的。对于COMS而言,这个电阻的阻值可以是1M以上,对于TTL则是需要视情况而定。最好的办法是看看芯片的数据手册,确认芯片晶振电路内部是否有电阻,如果没有,电路设计时最好加上。

晶振电路3

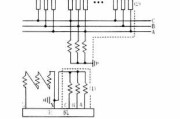

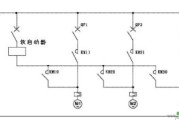

图3是有源晶振电路。

图3 有源晶振电路

有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。有源晶振不需要CPU的内部振荡器,连接方式相对简单(主要是做好电源滤波,通常使用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较差,而且价格高。

相关文章

发表评论